Bit-shifting register device and bit-shifting register

A shift register and low-potential technology, applied in static memory, digital memory information, instruments, etc., to achieve the effect of reducing manufacturing cost and reducing circuit size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

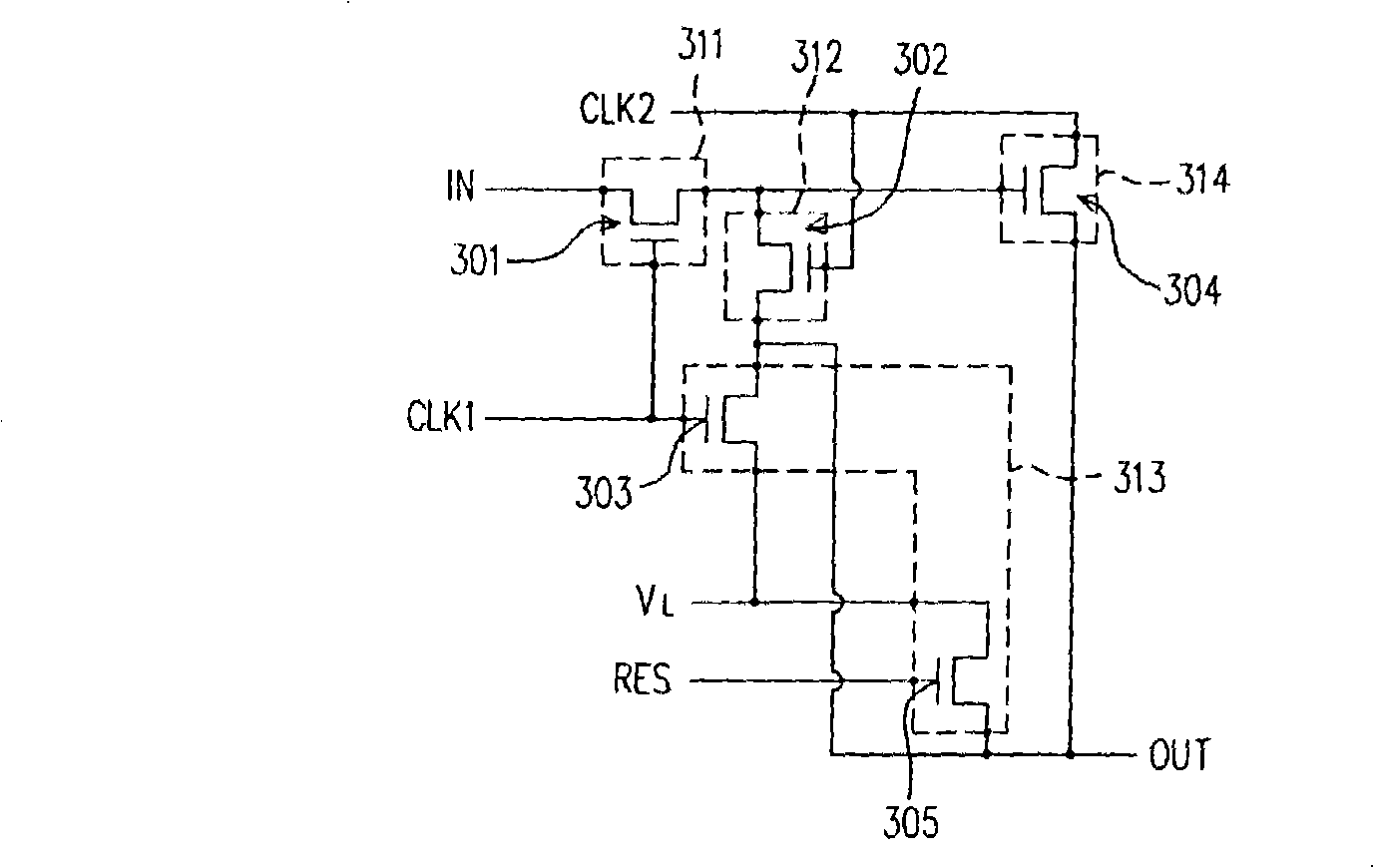

[0030] image 3 This is the shift register of the first embodiment of the present invention. The shift register includes an input unit 311, a feedback unit 312, a reset unit 313, and an output unit 314. In this embodiment, each unit is composed of at least one switch. For example, the input unit 311 includes a switch 301, the feedback unit 312 includes a switch 302, the reset unit 313 includes switches 303 and 305, and the output unit 314 includes a switch 304. The switches 301 to 305 all have a first terminal, a second terminal, and a control terminal, and these switches all determine whether to turn on or not according to the signal received by the control terminal.

[0031] The first terminal of the switch 301 of the input unit 311 receives an input signal IN, and the control terminal thereof receives a clock signal CLK1 (ie, the first signal) to determine whether to conduct the input signal IN to the second terminal. The first terminal of the switch 304 of the output unit 314...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com