Array processor structure

A technology of array processors and processor units, applied in architecture with multiple processing units, electrical digital data processing, instruments, etc., can solve the problems of DSP waste, difficult to determine the number of DSPs, high research and development costs, etc., and achieve data transmission Flexible, easy to implement quickly, and short design cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The features and advantages of the present invention will be described in detail with reference to the accompanying drawings.

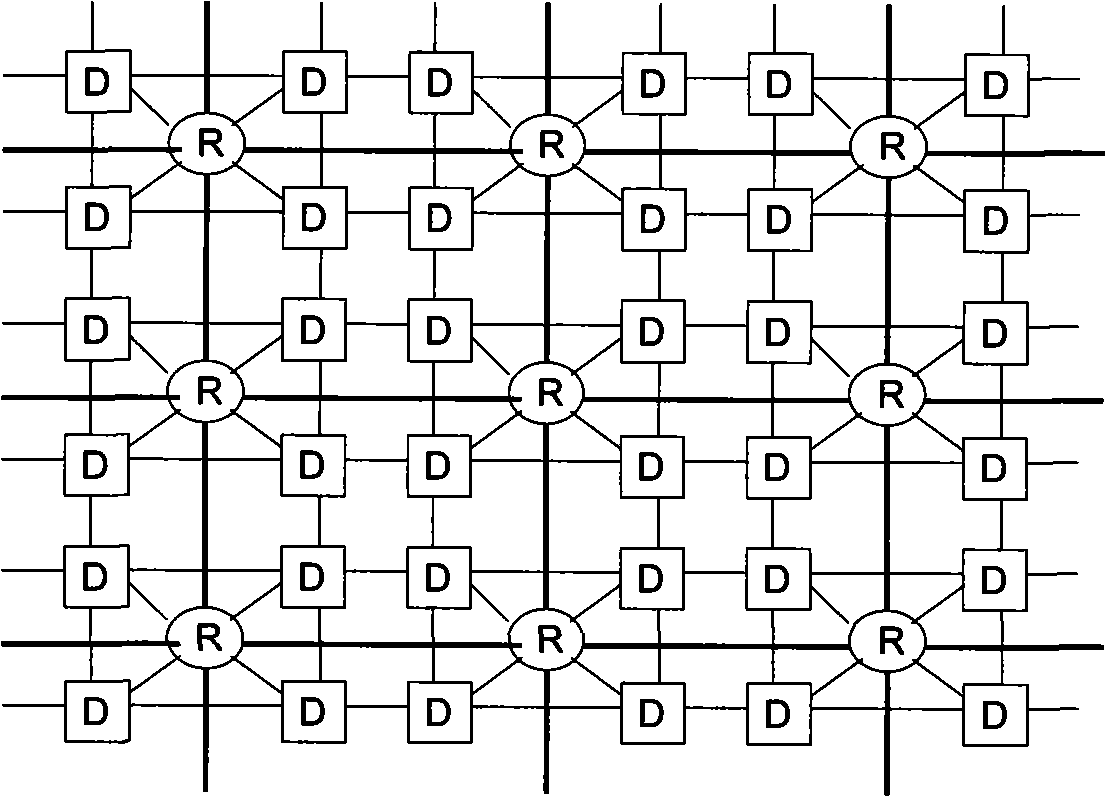

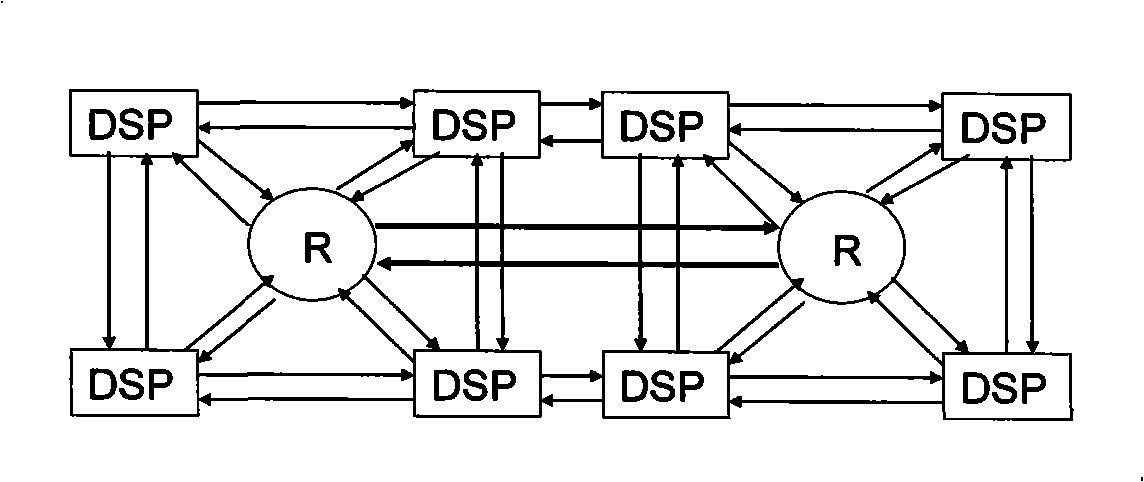

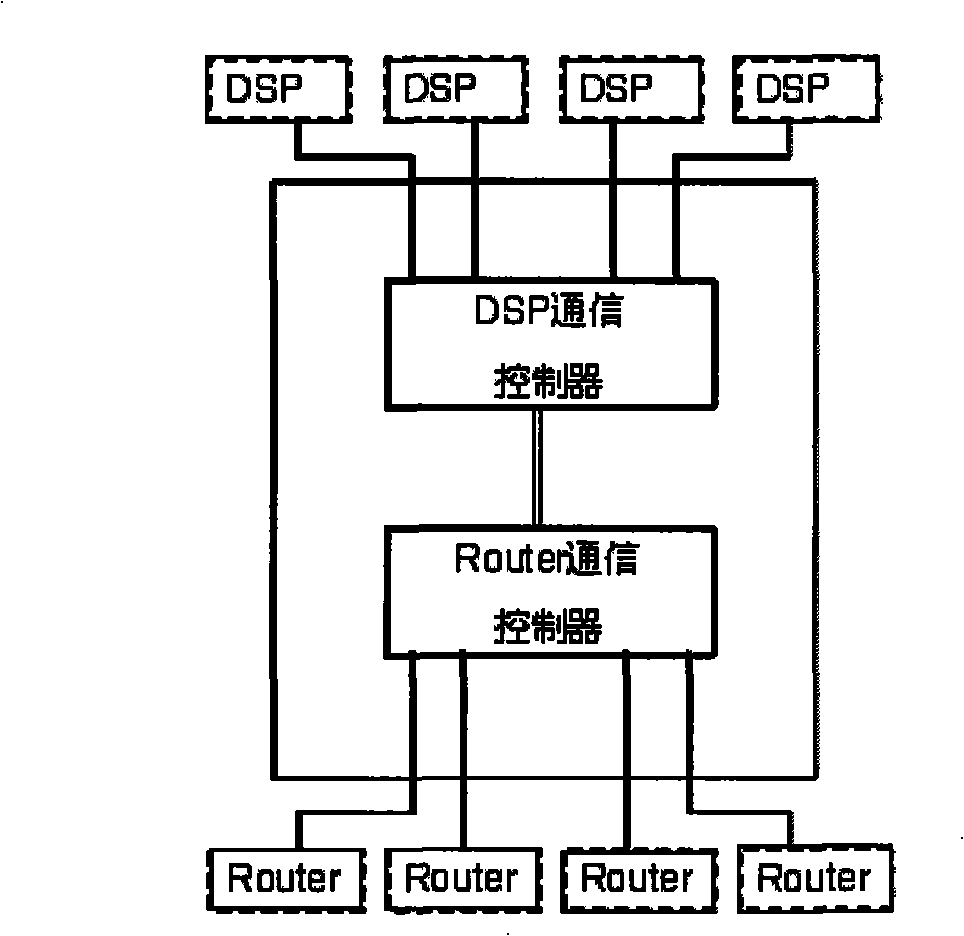

[0026] Such as figure 1 As shown, the array processor structure includes multiple processor units and multiple routing units (marked by R in the figure), and the processor unit in this embodiment adopts DSP (marked by D in the figure). Each DSP is a DSP array with a square grid structure arranged in rows and columns adjacent to each other through an interconnection bus, and each routing unit R is also arranged in a row and column adjoining a square grid structure routing array through an interconnection bus , its rows and columns are distributed alternately with the rows and columns of the DSP array. In one embodiment, each DSP has five input / output ports, and the input / output ports of the DSPs on the non-array boundary are five, four of which are connected to the corresponding ports of the adjacent four DSPs, and the remaining One connects t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More