Method for judging wafer thinning, device structure and device and its manufacture method

A device structure and wafer technology, applied in the direction of manufacturing tools, grinding devices, surface polishing machine tools, etc., can solve problems such as delays in the grinding process and reduction in process output

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

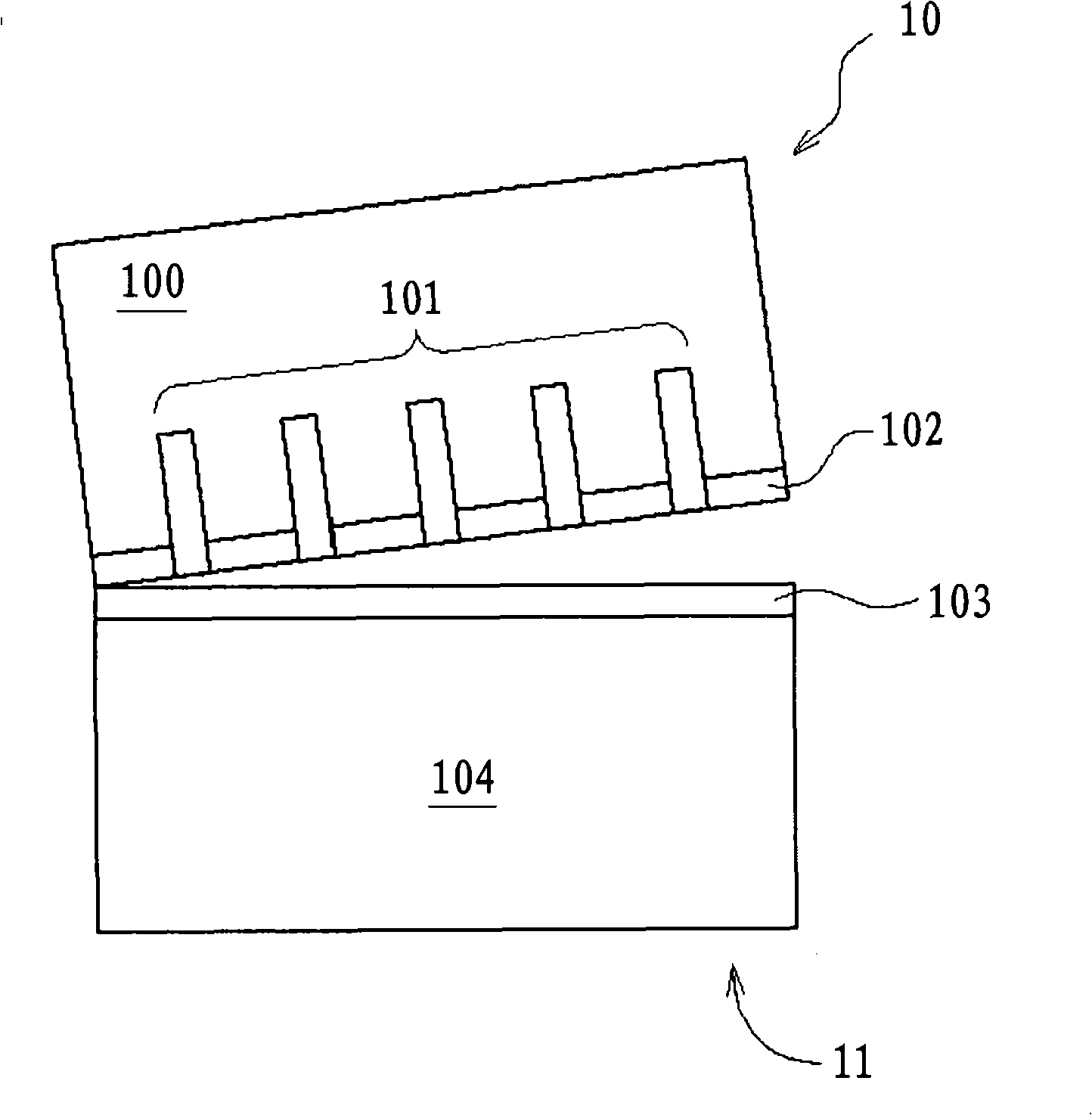

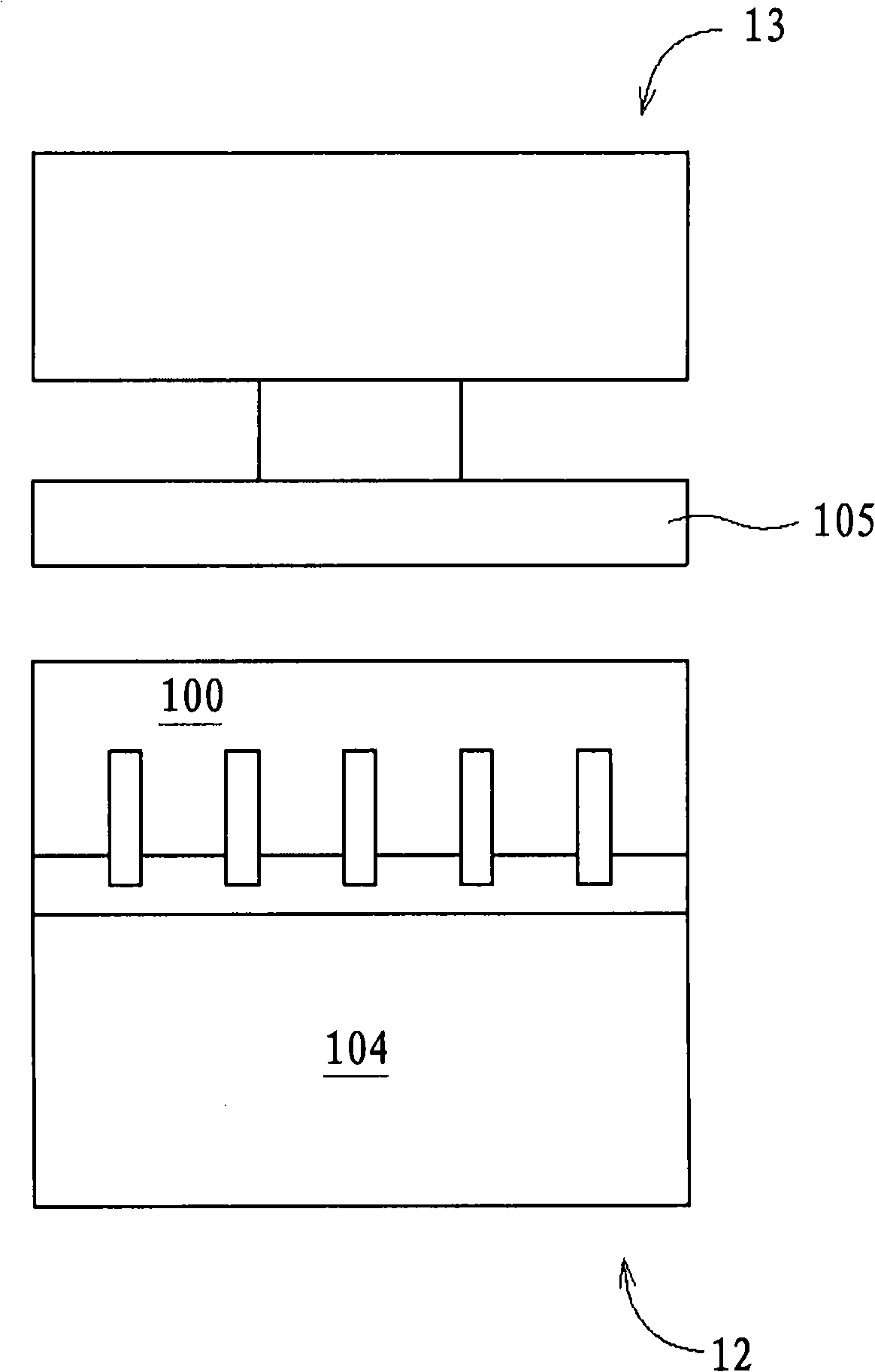

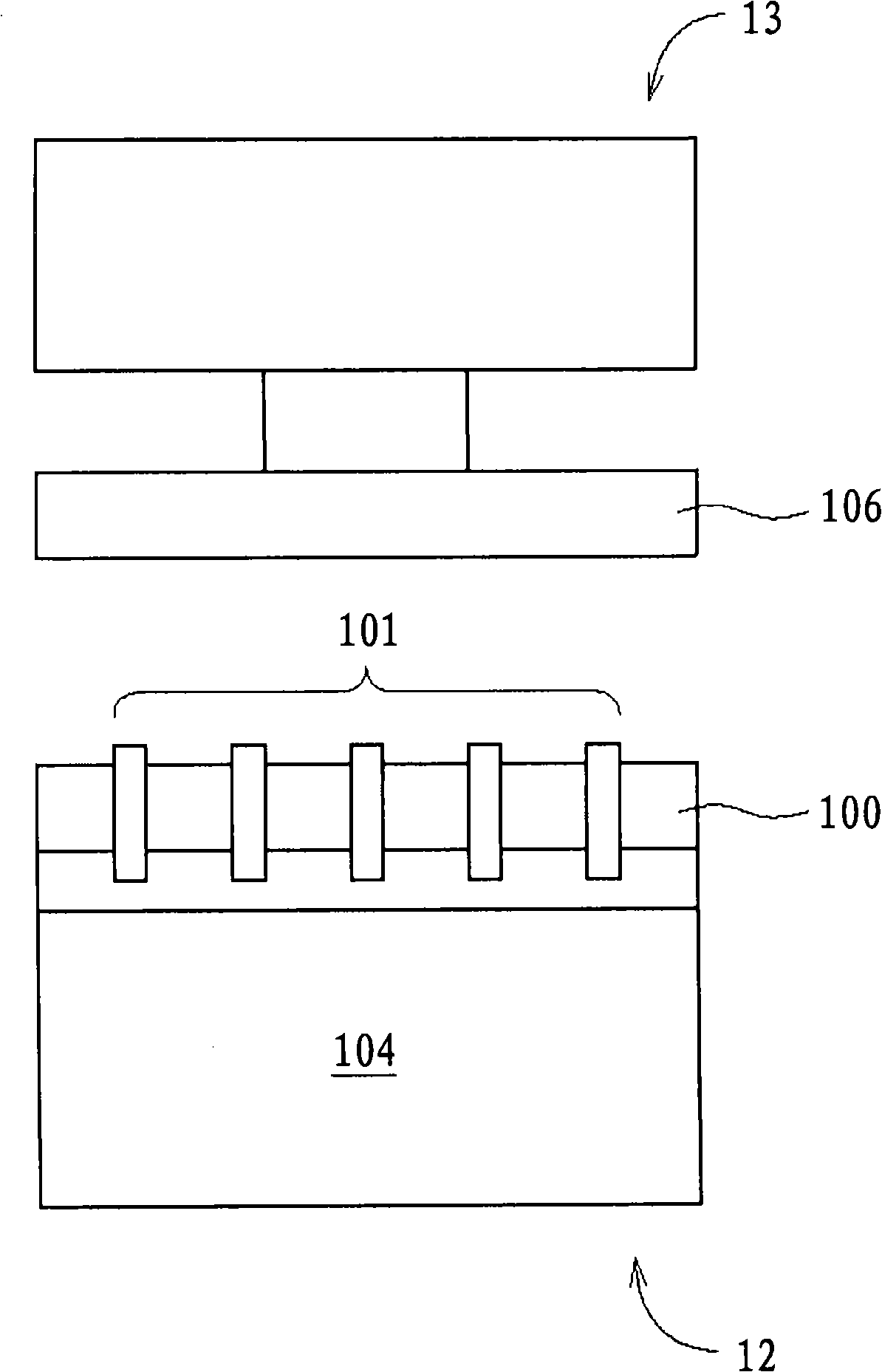

[0087] In order to further explain the technical means and effects adopted by the present invention to achieve the intended purpose of the invention, the method, device structure, mechanism and manufacturing thereof for judging wafer thinning proposed according to the present invention will be described below in conjunction with the accompanying drawings and preferred embodiments. The specific implementation, structure, method, steps, features and effects of the method are described in detail below.

[0088] The making and utilizing of preferred embodiments of the invention are discussed in detail below. It should be appreciated, however, that the present invention provides many applicable inventive concepts, which can be embodied in a wide variety of specific contexts. The specific embodiments discussed below are only used to illustrate the manufacture and utilization of the present invention in specific ways, and are not intended to limit the scope of the present invention. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More