Signal receiver

A technology for controlling signals and receiving circuits, which is applied in the field of receiving circuits, and can solve problems such as the unbalanced duty cycle of the output voltage Vout

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

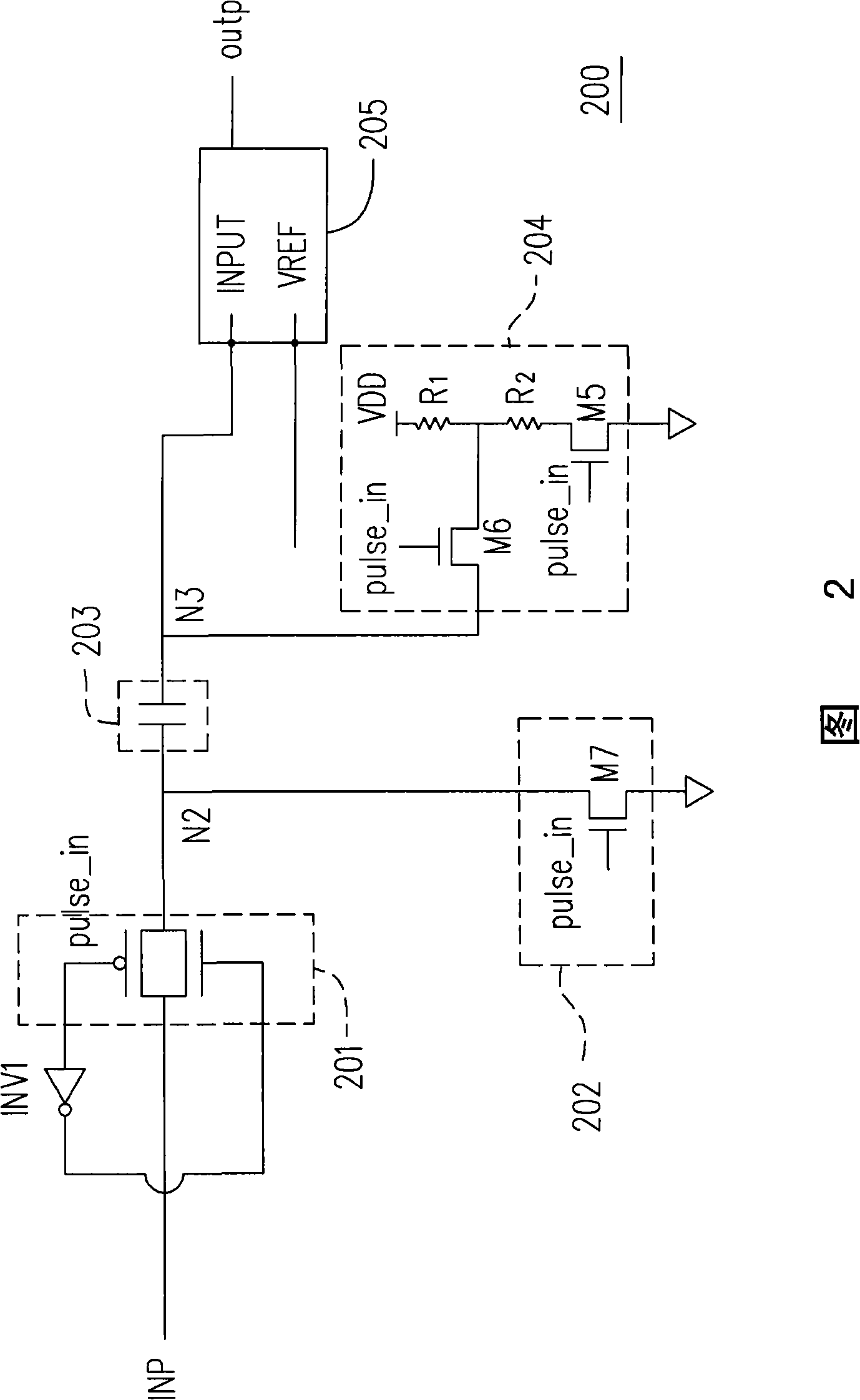

[0036] figure 2 is a receiving circuit according to an embodiment of the present invention. The receiving circuit 200 includes: a transmission gate 201 , a pull-down unit 202 , a boost capacitor 203 , a voltage dividing unit 204 and a receiving unit 205 .

[0037] The transmission gate 201 determines whether to conduct the input signal INP according to the control signal pulse_in. Of course, this embodiment is not limited thereto, and the transmission gate 201 may also have other appropriate structures. The input terminal of the transmission gate 201 inputs the signal INP, the output terminal is connected to the node N2, the first control terminal is connected to the control signal pulse_in, and the second control terminal is connected to the output terminal of the inverter INV1 (that is, the inverter receiving the control signal pulse_in phase signal).

[0038] When the control signal pulse_in is logic high, the transmission gate 201 will not conduct the input signal INP ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More