Apparatus and method for preventing snap back in integrated circuits

A circuit, bias circuit technology, applied in the direction of electrical components, generation of electrical pulses, reliability improvement and modification, etc., can solve problems such as backup current flow, data corruption, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0008] Those skilled in the art will realize that the following description of the invention is illustrative only and not limiting in any way. Other embodiments of the invention will be readily apparent to those skilled in the art.

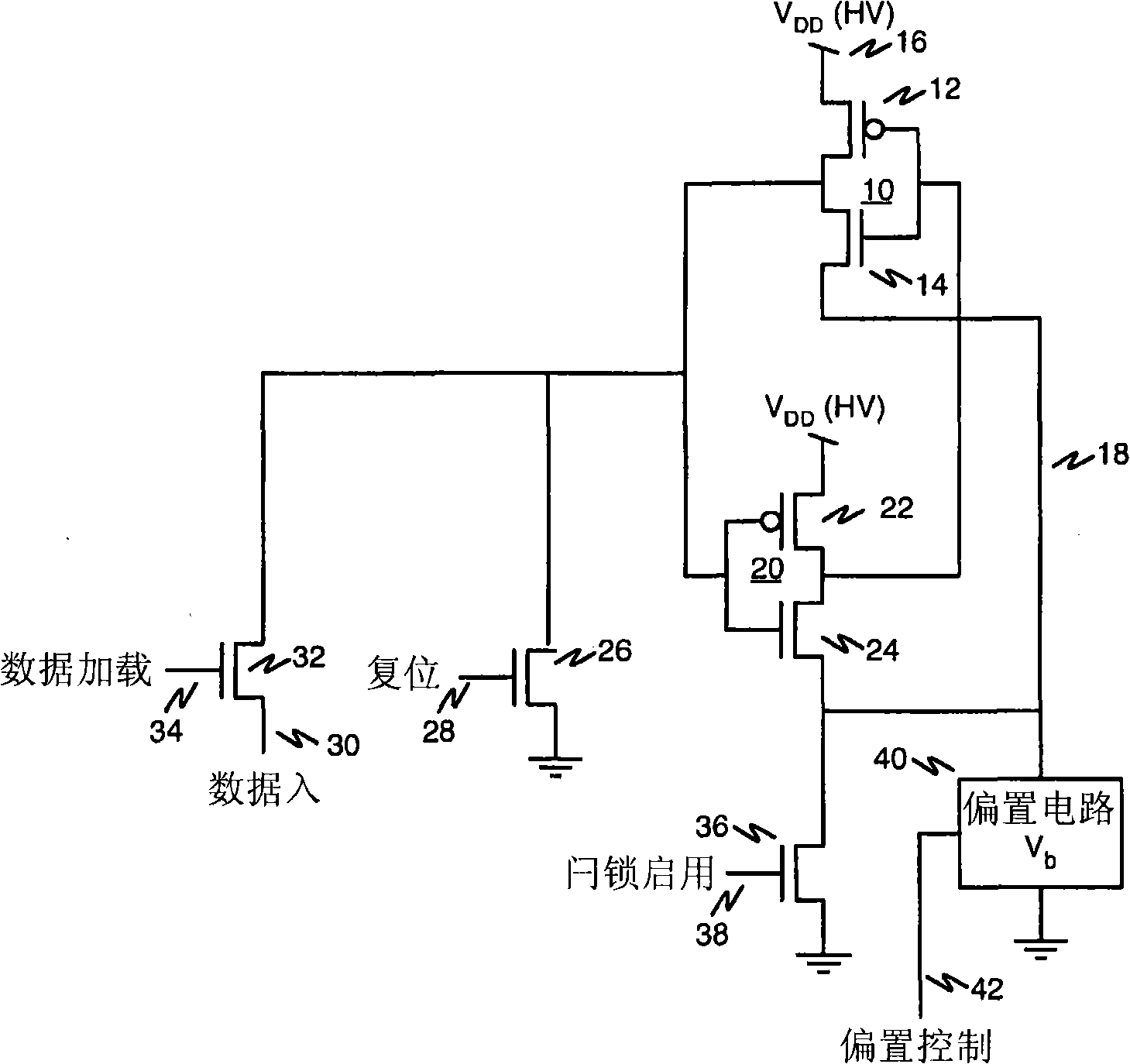

[0009] According to an illustrative example of a device according to the invention, such as figure 1 As shown in , the first inverter 10 includes a P-channel MOS transistor 12 connected in series with an N-channel MOS transistor 14 at the high voltage source V HV (shown at reference numeral 16 ) (eg 16V) and source node 18 . The gates of transistors 12 and 14 are coupled together. The second inverter 20 includes a P-channel MOS transistor 22 connected in series with an N-channel MOS transistor 24 between the high voltage source 16 and the source node 18 . The gates of transistors 22 and 24 are coupled together. Transistors 12, 14, 22 and 24 are high voltage transistors, ie transistors designed to have a breakdown voltage higher than the VDD vo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More