Buffer cell circuit for resisting single-particle transient state

A single-event transient and buffer technology, which is applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc., can solve the problems of high overhead of area and power consumption, and achieve area and power consumption The effect of small loss, high speed and simple circuit structure

Inactive Publication Date: 2010-11-10

BEIJING MXTRONICS CORP +1

View PDF0 Cites 6 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Triple-mode redundancy plus majority voting can completely eliminate the effect of single-event transients (or fault signals), but it will bring extremely high overhead (>200%) in area and power consumption

However, the cost of power consumption and area is unaffordable

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment Construction

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

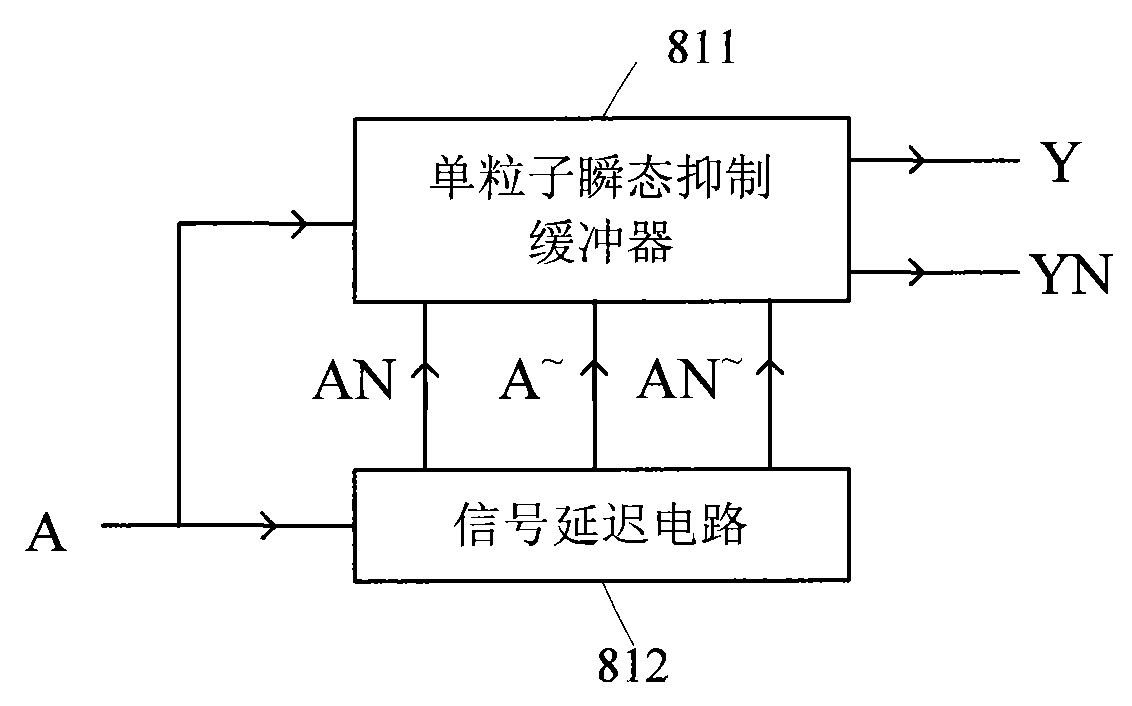

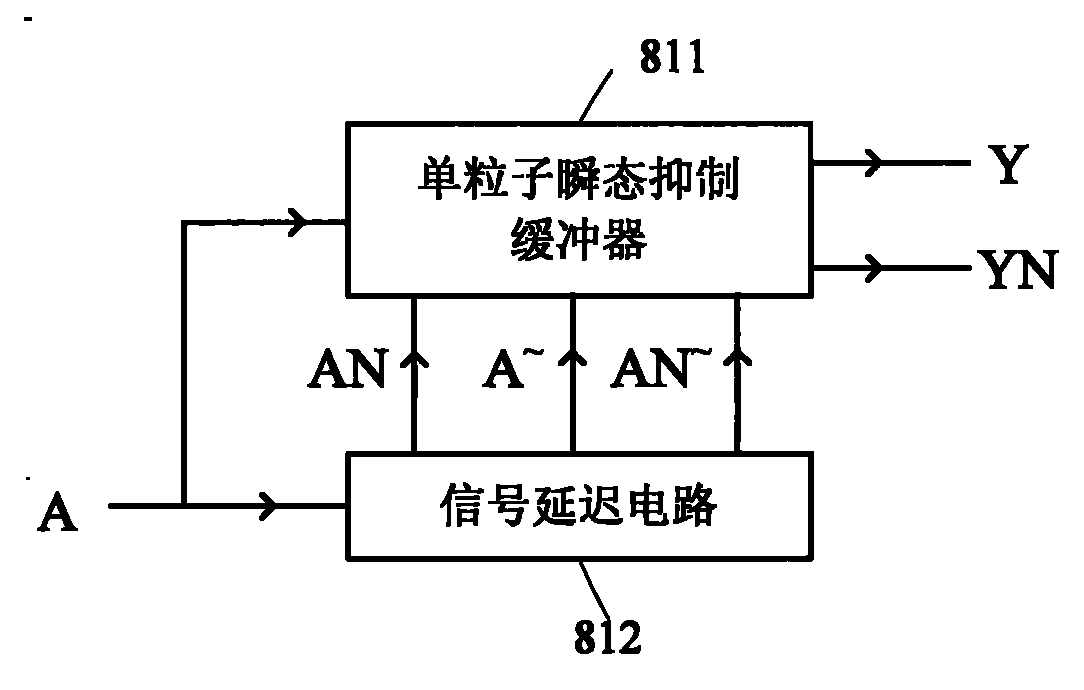

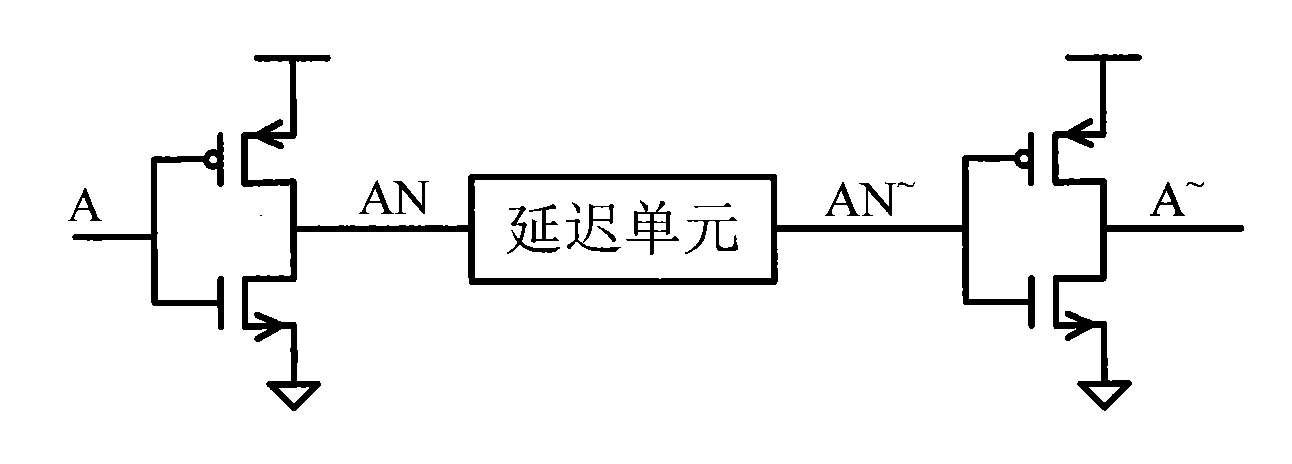

The invention relates to a buffer cell circuit for resisting the single-particle transient state which mainly consists of a single-particle transient-suppression buffer circuit and a signal-delay circuit, wherein, the signal-delay circuit consists of an inverter and a delay unit, the single-particle transient-suppression buffer circuit is an N-shaped single-particle transient-suppression buffer circuit or a P-shaped single-particle transient-suppression buffer circuit. With the adoption of the buffer circuit of the invention, the single-particle transient pulse which is generated on an input signal and provided with a pulse width smaller than the delay time internally set in a buffer, is eliminated, and key signals such as a clock, a reset, data, and the like, are effectively protected. At the same time, the buffer also possesses the strong ability for resisting single-particle transient state. In addition, The design for a circuit resisting single-particle is reinforced by adopting the buffer cell circuit for resisting the single-particle transient state, so that the area caused by the reinforcement of single-particle resistance and the power consumption are remarkably reduced compared with the common reinforcing methods, such as the triple modular redundancy, and the like.

Description

An anti-single event transient buffer unit circuit technical field The invention relates to a buffer unit circuit, in particular to a buffer unit circuit capable of eliminating and suppressing single-event transient pulses. Background technique Radiation produced by high-energy protons or high-energy neutrons hitting atomic nuclei and heavy nuclear particles in cosmic rays can cause circuit state changes, such as transient pulses in combinatorial logic, bit flips in memory-like cells, etc. This effect is a single particle The result of the action is often called a single event effect. Single event effects can be divided into single event upset (SEU), recoverable single event latch (SEL), single event transient (SET) and other single event soft errors, and also include single event burn (SEB), single event Hard errors such as particle gate breakdown (SEGR), unrecoverable single event latch-up (SEL), etc. The most sensitive part to the single event effect in the early int...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Patents(China)

IPC IPC(8): H03K19/0185

Inventor 边强岳素格

Owner BEIJING MXTRONICS CORP