System and method for electric test of semiconductor wafer

一种半导体、电测试的技术,应用在电子电路测试、非接触式电路测试、单个半导体器件测试等方向,能够解决影响集成电路电特征等问题,达到消除干扰的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

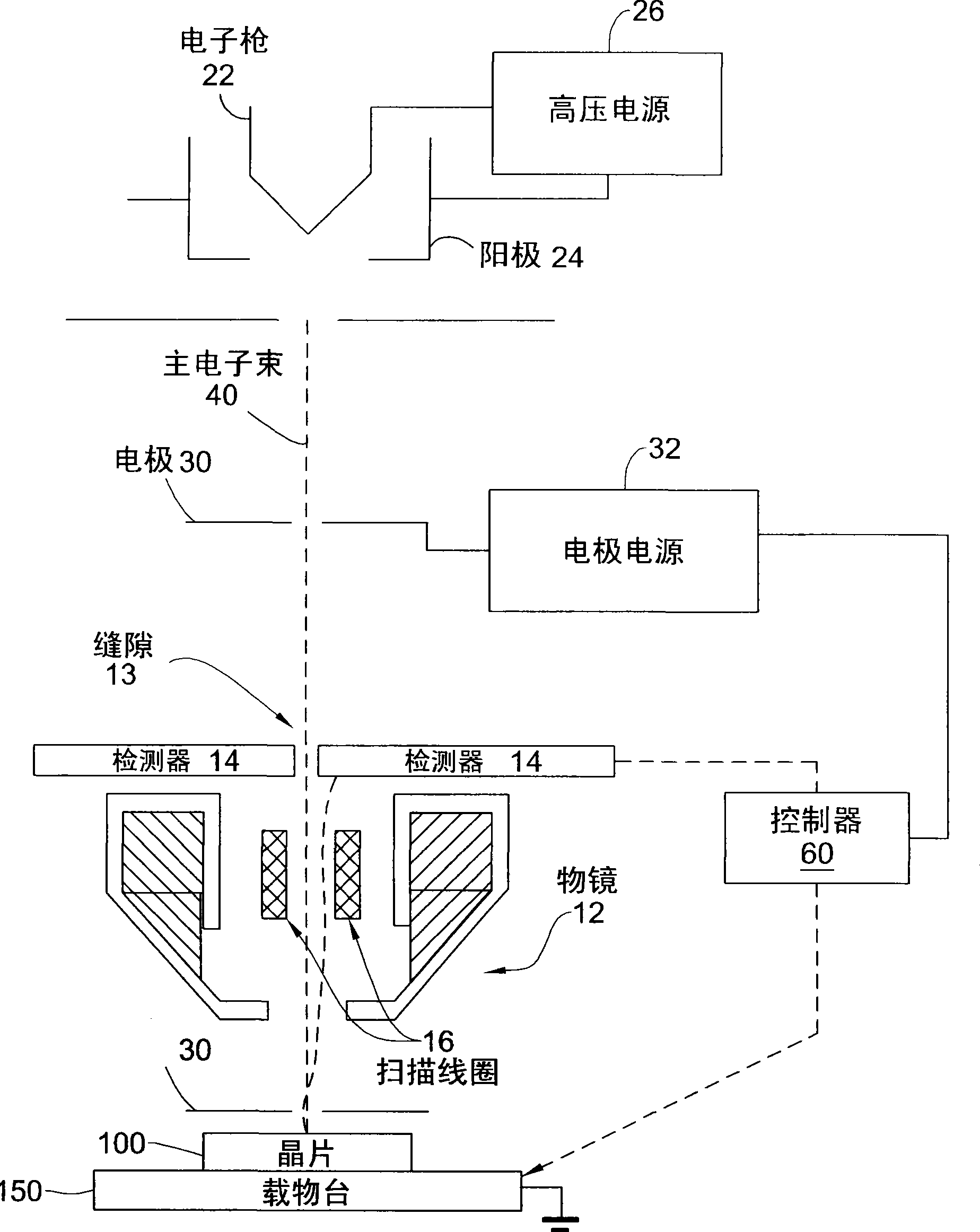

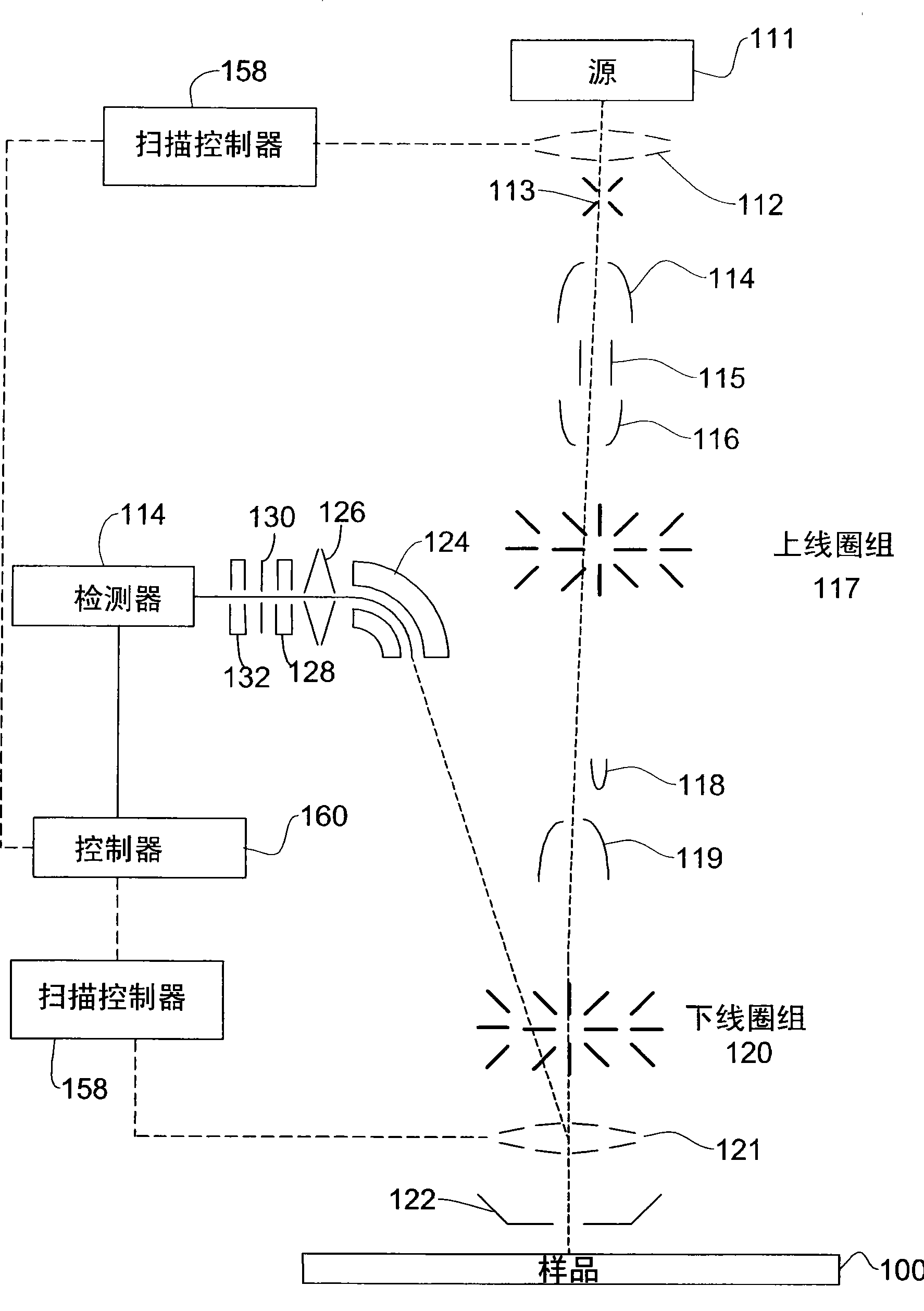

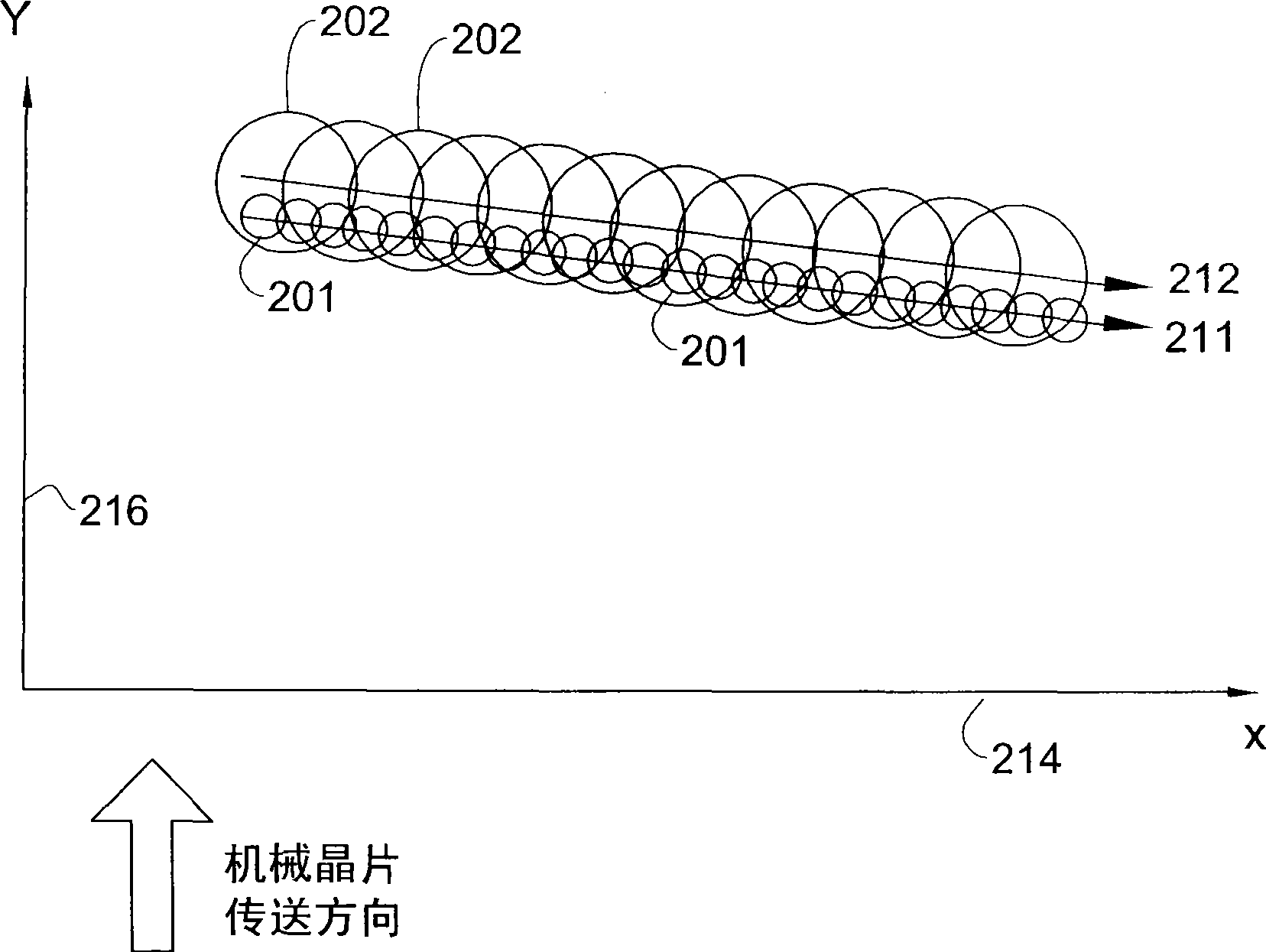

[0059] The following description relates to charged particle microscopes, such as scanning electron microscopes (SEM), especially step and repeat type SEMs. In charged particle microscopes, it is usually done by scanning an area of the wafer (determined by the field of view of the SEM). Area) and mechanically introduce relative motion between the wafer and the SEM to advance the repeated steps of scanning another area to scan the wafer. For example, the relative movement can be achieved by an electrostatic field and / or a magnetic field introduced by different electrostatic and / or magnetic elements such as lenses, deflectors, etc. It should be pointed out that other charged particles and even photons can be used to detect voltage contrast. It should also be pointed out that the present invention can also be implemented by introducing a substantially constant movement between the SEM and the wafer. The relative movement can be linear or even rotational, and / or any combination of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More