High speed serializer/deserializer transmit architecture

A converter and flip-flop technology, applied in the field of communication systems, can solve the problems of increasing waveforms, increasing the waiting time of pipeline triggers, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] Various embodiments will now be described with reference to the drawings, wherein like reference numerals are used to represent like elements throughout. In the following description, for purposes of explanation, numerous specific details are set forth in order to provide a thorough understanding of one or more embodiments. It may be evident, however, that the embodiments may be practiced without these specific details. In other instances, well-known structures and devices are shown in block diagram form in order to facilitate describing one or more embodiments.

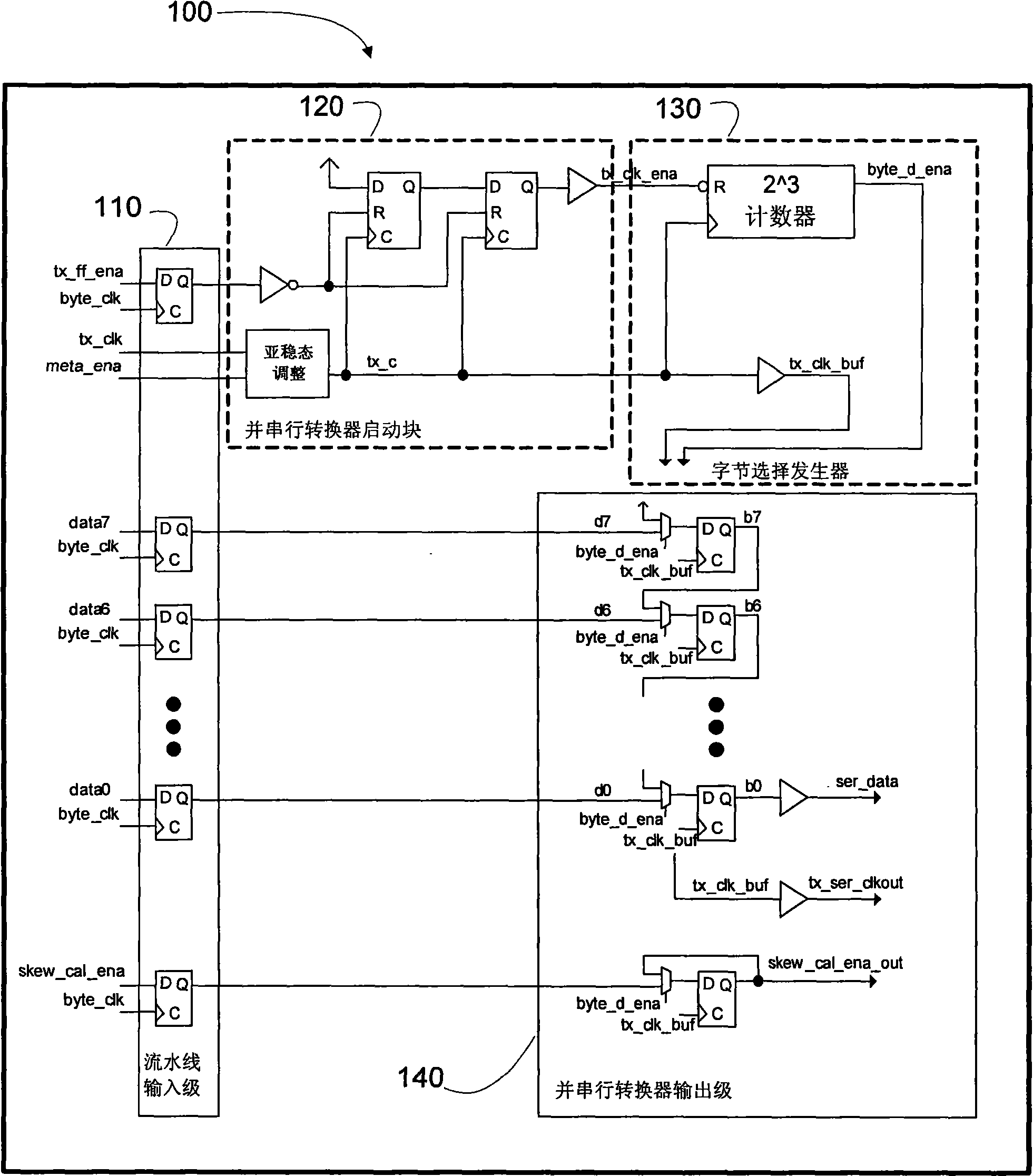

[0014] In one embodiment, the parallel-to-serial converter circuit 100 includes an figure 1 The following circuit is depicted in:

[0015] Pipeline Input Stage 110: This is a set of registers that enables easy timing closure of data bits from the core to the MDDI Host PHY. It fetches 8 bits of parallel data from the core and latches them using the core byte_clock. The first host and the external host have ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More