Insulated gate semiconductor device

An insulated gate type, n-type semiconductor technology, used in semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of reducing the area of the action area, expanding the chip size, and increasing the area occupied by the protection diode. The effect of reducing the occupied area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

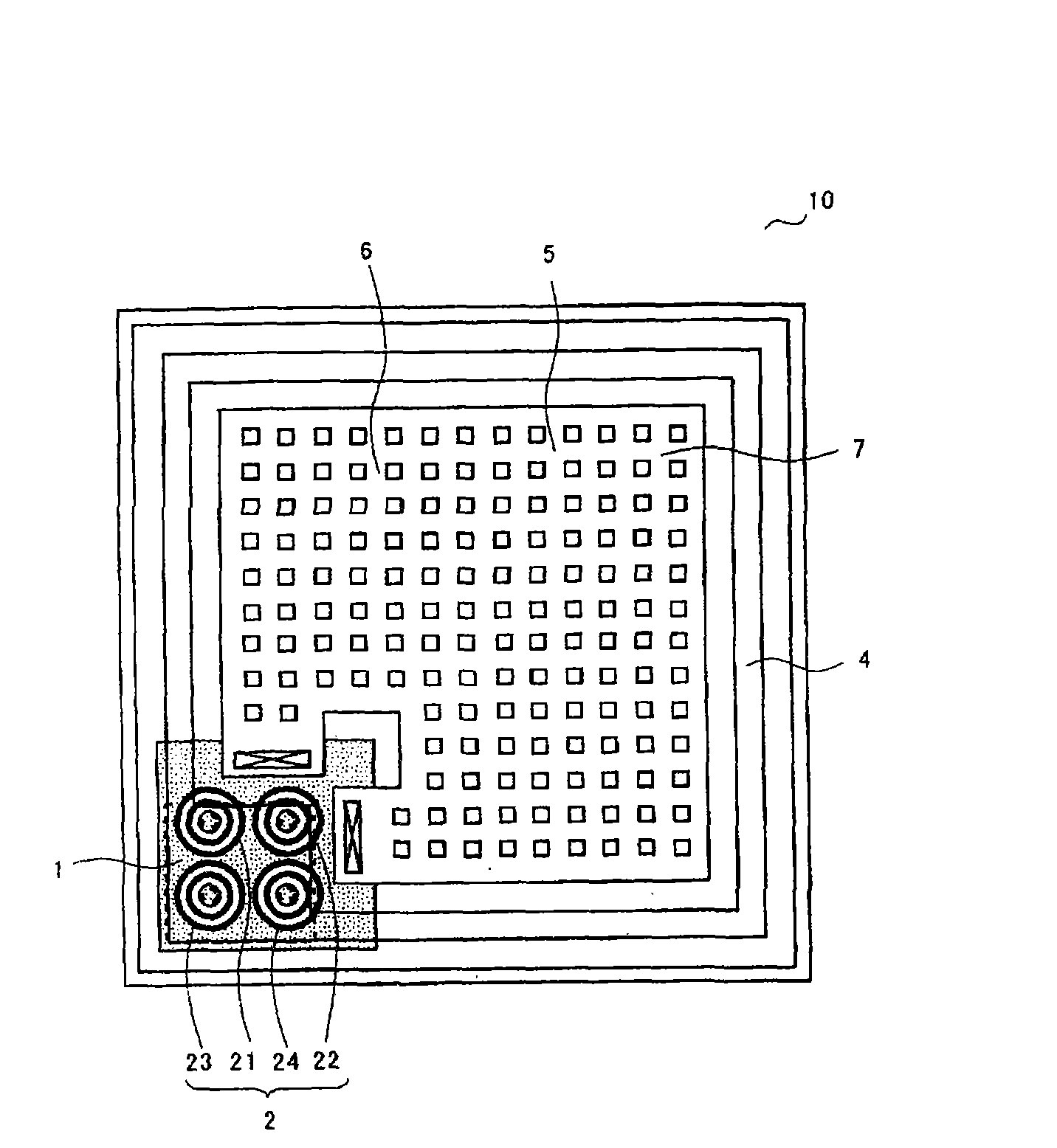

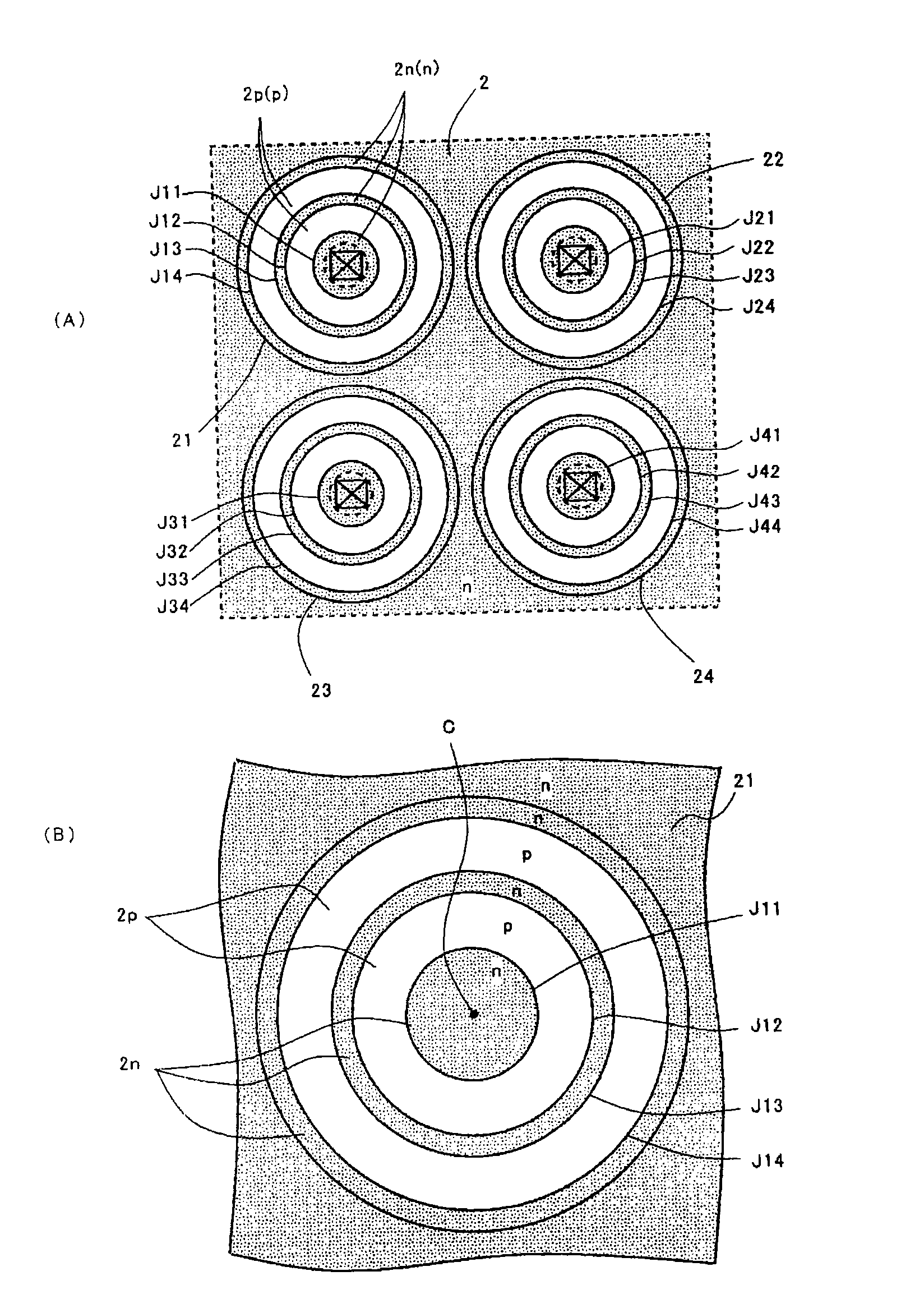

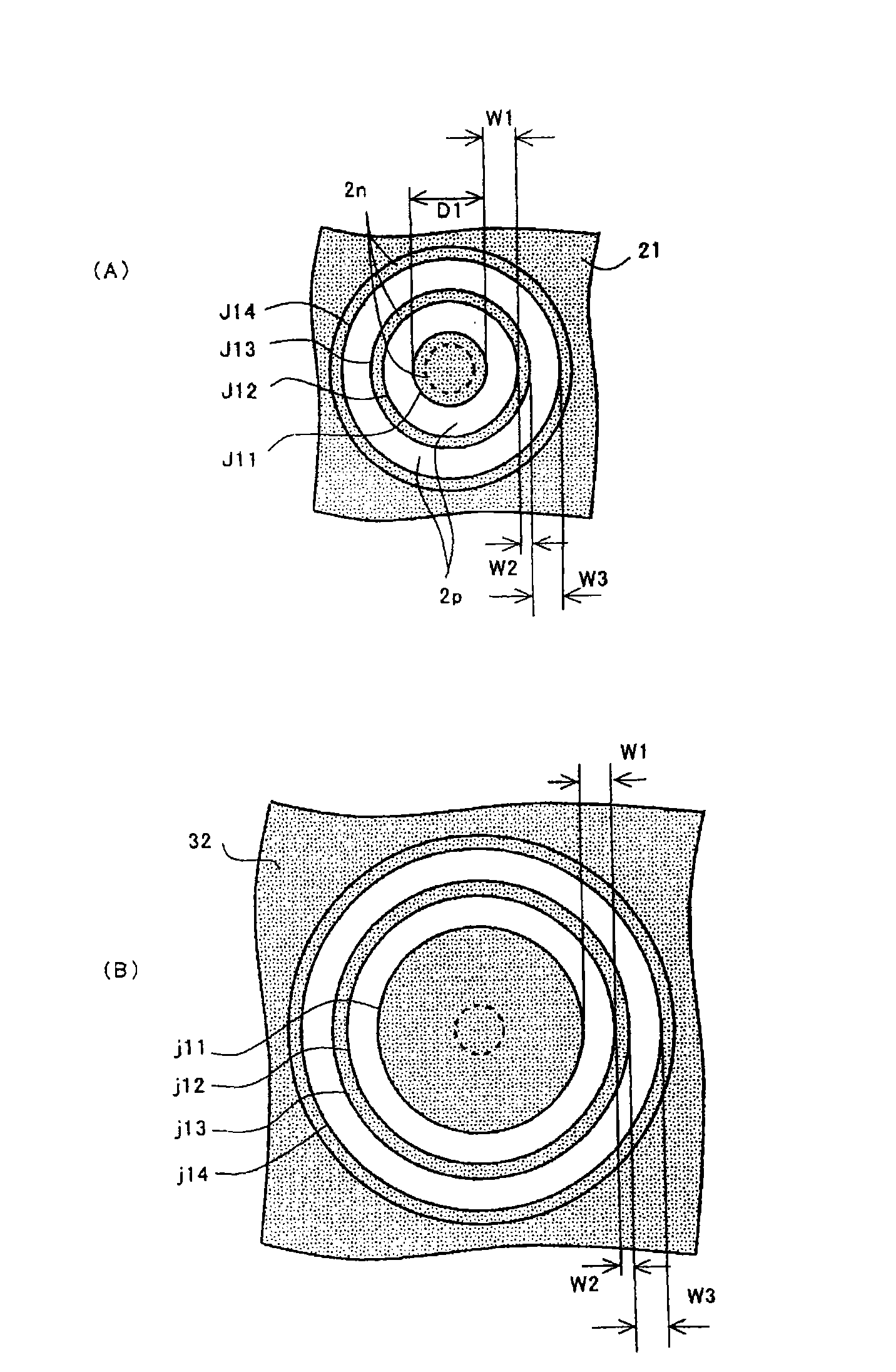

[0064] refer to Figure 1 to Figure 19 , the embodiment of the present invention will be described by taking the case where a transistor unit of a MOSFET is provided in an operating region as an example.

[0065] First, refer to Figure 1 to Figure 8 The first embodiment will be described. figure 1 It is a plan view showing the MOSFET of this embodiment.

[0066] The MOSFET has a gate electrode 1 , a protection diode group 2 and an operating region 5 .

[0067] A plurality of MOS transistor cells 6 are arranged in the operating region 5 . Hereinafter, the operating region 5 refers to a region where the MOS transistor unit 6 is arranged. The gate pad electrode 1 is arranged, for example, outside the operating region 5 , and is connected to the gate electrode of each MOS transistor cell 6 via a gate connection electrode 4 arranged around the operating region 5 .

[0068] The MOS transistor cell in the operating region 5 has a known structure, so it is omitted from the illust...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More