Multi-BIOS mapping parallel initialization method

An initialization and image technology, applied in the direction of program loading/starting, program control devices, etc., can solve the problems of overall efficiency reduction, failure to improve system performance and efficiency, etc., and achieve the effect of improving efficiency, improving high availability, and broad application prospects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

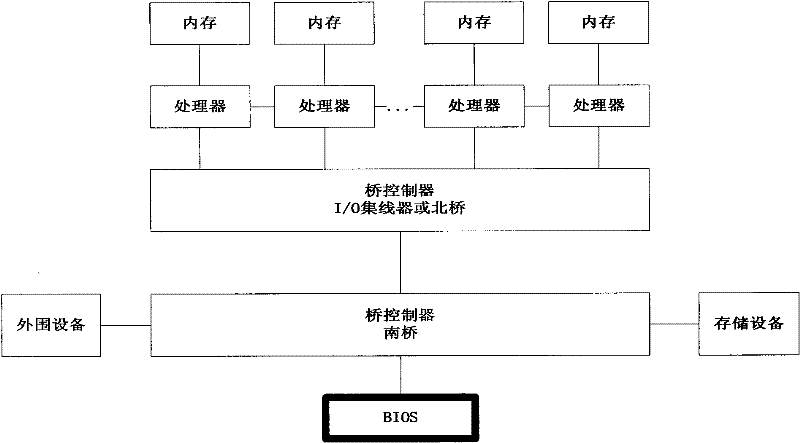

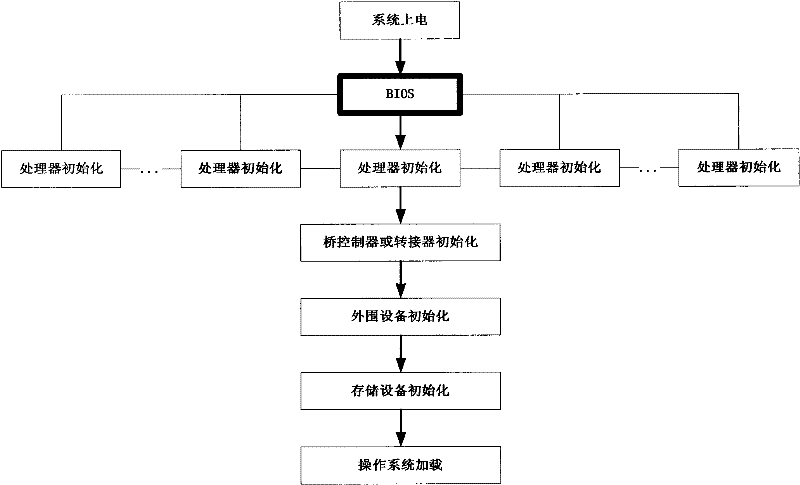

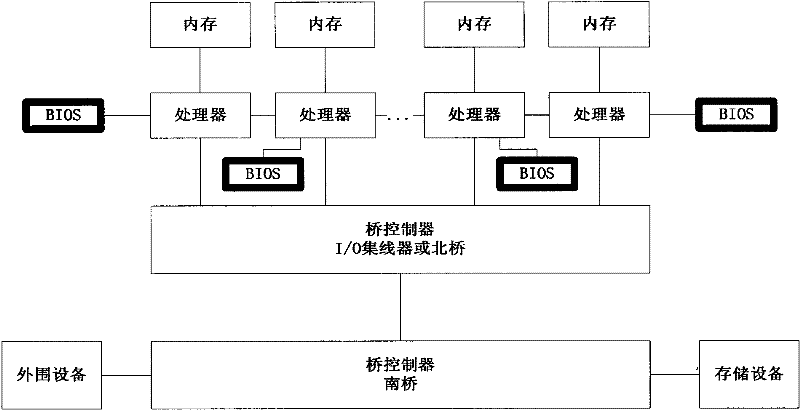

[0039] The method of the present invention mainly comprises: multiple BIOS images (1), parallel initialization system (2), directly connected processor (3), therefore specifically describe the realization of the appeal method with the system structure of a high-performance computer, this high-performance computer Mainly include: BIOS module (A), processor module (B), memory module (C), bridge controller or adapter module (D), peripheral device (I / O) module (E) and storage module (F ).

[0040] Therefore, the architecture of this system is: image 3 The BIOS image is directly connected to the processor module through the SPI (or LPC) bus or other communication protocols, or it can be connected through an adapter chip between the processor module and the BIOS image. The processor module integrates a memory controller, The processor module is connected to the bridge controller or the adapter through the point-to-point communication protocol or the system bus, and the multi-level...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More