Device and method for instruction scheduling

An instruction scheduling and instruction technology, applied in machine execution devices, concurrent instruction execution, etc., can solve problems such as reduced pipeline efficiency, instructions cannot be issued, reduced pipeline utilization, processor performance, etc., to achieve the effect of improving efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

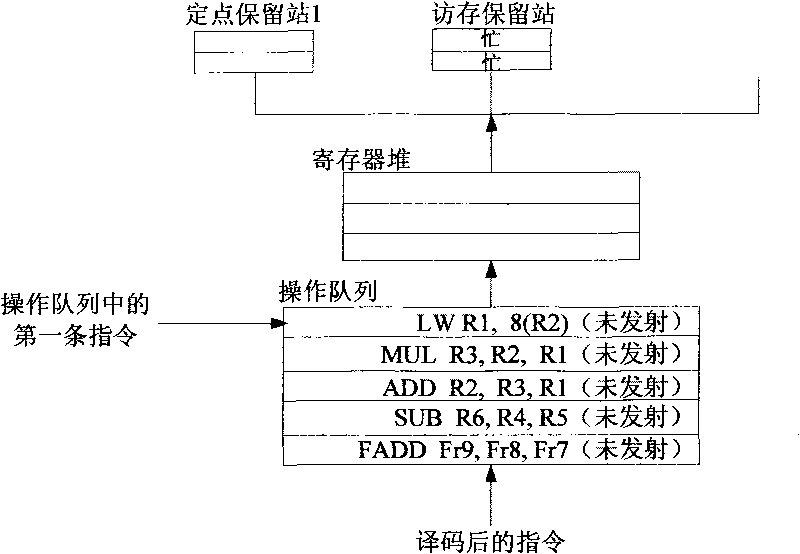

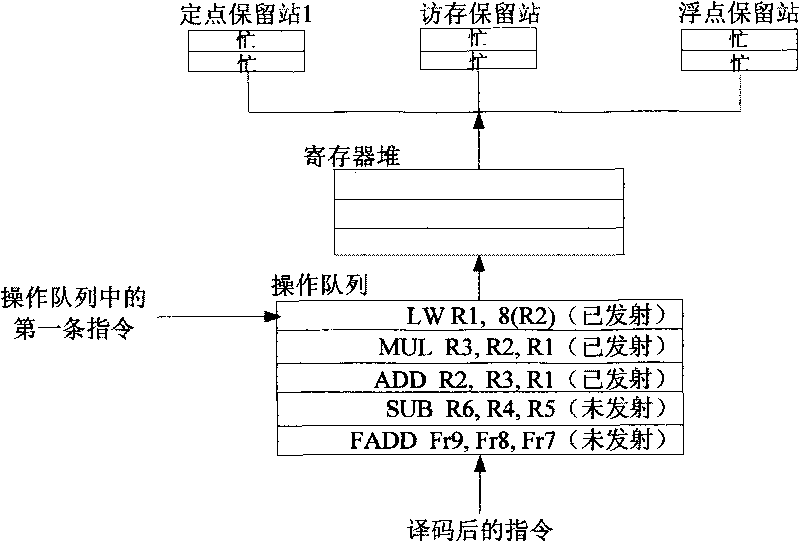

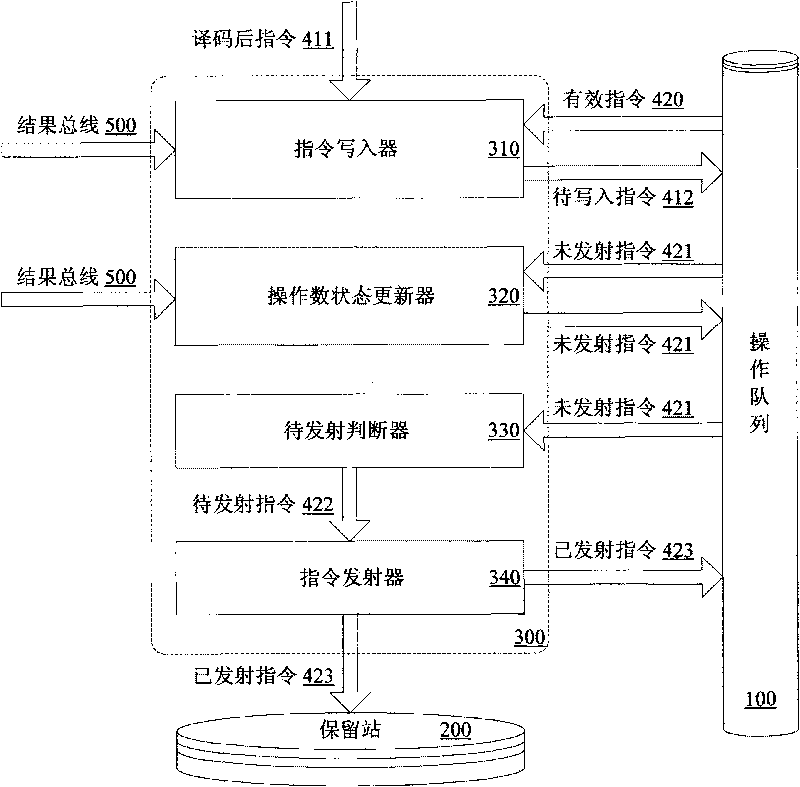

[0024] As mentioned above, the present invention aims to solve the problem of low instruction emission efficiency in the prior art in which the reservation station intercepts the result bus and dynamically schedules instructions according to the interception result, and provides an instruction scheduling technology to improve The efficiency of the instruction issue pipeline and the overall performance of the microprocessor. The main idea of this instruction scheduling technology is, based on the data correlation between instructions, when there are idle items in the reservation station, select the instruction with all operands ready to send to the reservation station, thus effectively improving the pipeline efficiency of instruction issuance .

[0025] The above and other technical features and beneficial effects of the present invention will be more fully explained through the introduction of preferred embodiments with reference to the accompanying drawings.

[0026] ima...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More