Method for manufacturing alignment mark of semiconductor silicon wafer and semiconductor silicon wafer thereby

A silicon wafer alignment and manufacturing method technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problem of insufficient use of cutting lanes, the influence of alignment signal morphology, signal strength, and quasi-marking Shape changes and other issues, to achieve the effect of saving the use of area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

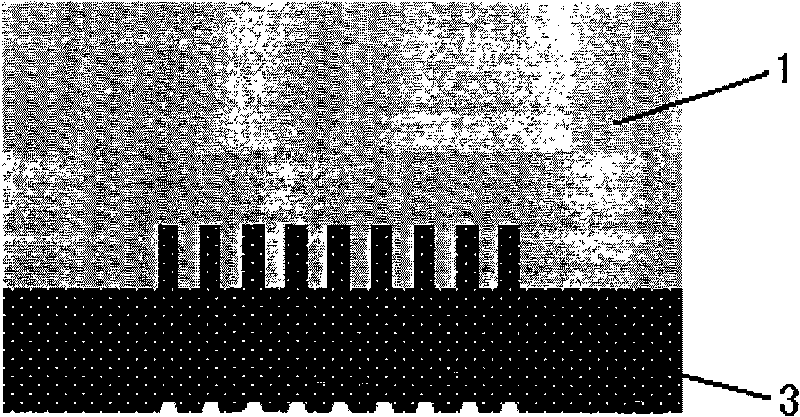

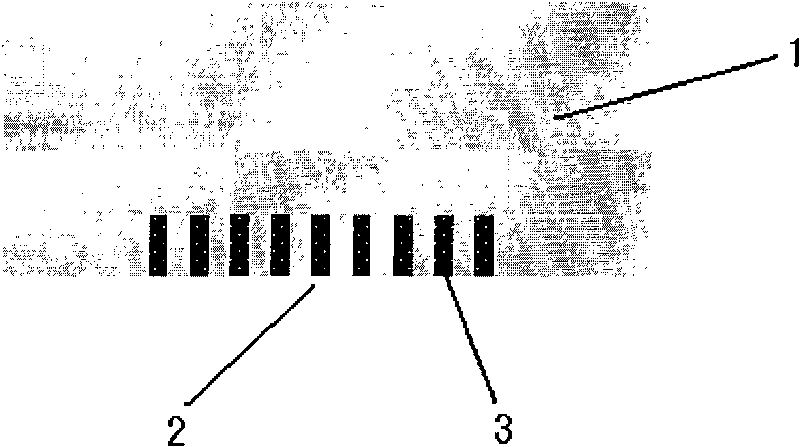

[0015] The invention discloses a method for manufacturing an alignment mark on a semiconductor silicon wafer, such as figure 2 As shown, before photolithography, a layer of luminescent material 3 is deposited on the back of the semiconductor silicon wafer 1, then photolithography is performed on the back of the silicon wafer, and the luminescent material layer is etched in the subsequent etching step to form Alignment mark 2, such as image 3 shown.

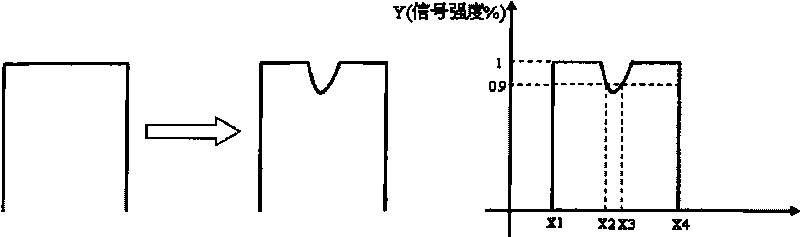

[0016] In the present invention, the alignment mark is made of luminescent material. The luminescent substance is added to the alignment mark, which greatly enhances the signal intensity of the peak. In this way, even if the bottom shape of the alignment mark is not good or there are residues, the signal intensity can be improved and the signal intensity can be reduced. Measurement error. Such as Figure 4 As shown, when the alignment mark is doped with a luminescent substance, the signal intensity of the alignment mark is m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More