Ion implantation zone forming method, MOS transistor and manufacture method thereof

A technology for MOS transistors and ion implantation regions, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve the problems of source/drain region overflow or punch-through electrical performance, deterioration, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

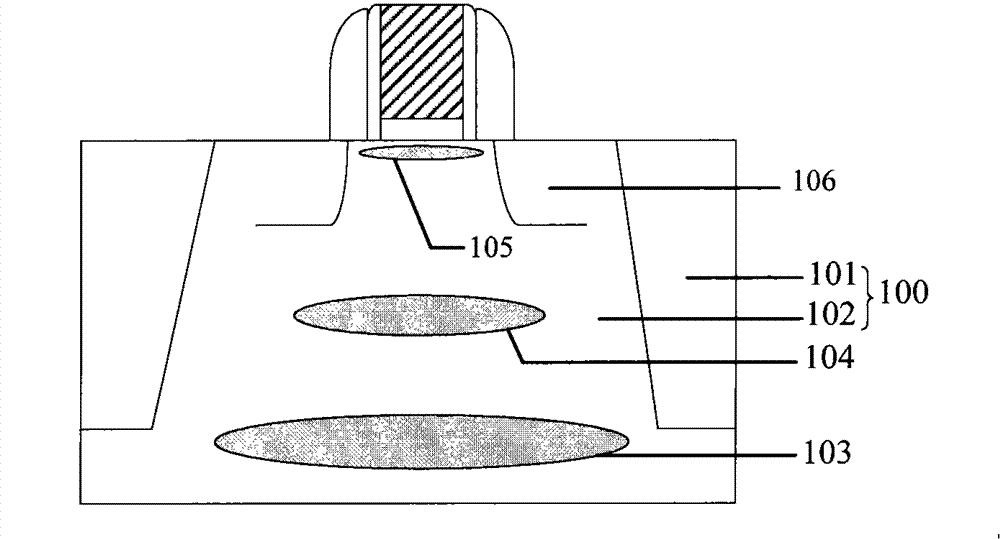

[0030] The inventors found that, because the existing MOS transistors use ultra-shallow junction technology to form source / drain regions to overcome the short channel effect, but the implanted ions in the source / drain regions will cause diffusion and penetration, which will cause the source / drain regions Junction capacitance and junction leakage lead to overflow or punch-through effect between source / drain regions, affecting the electrical quality of MOS transistors.

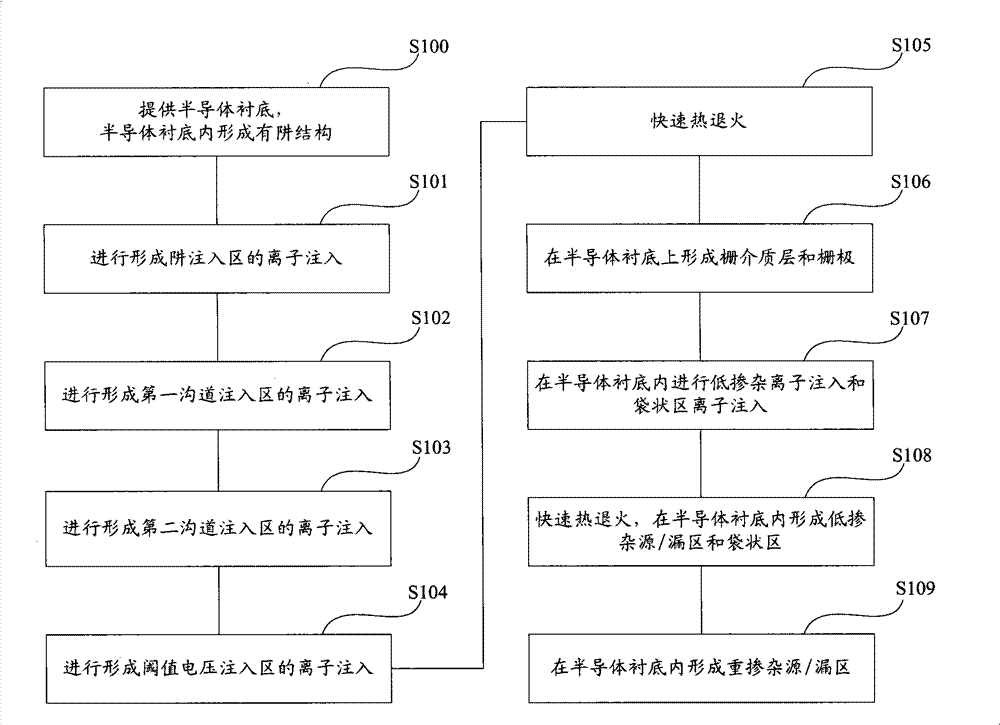

[0031] Therefore, when manufacturing MOS transistors, in order to prevent the occurrence of the above-mentioned defects. In the present invention, the ion implantation process is carried out in the well structure of the semiconductor substrate in order to form the well implantation region, the first channel implantation region, the second channel implantation region and the threshold voltage implantation region, wherein the second The channel implantation region is located between the source / drain regions to be ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More