Phase change memory

A phase-change memory and memory technology, applied in the field of memory and phase-change memory, can solve the problems of wasting the writing speed of phase-change memory, limiting the scope of use, etc., so as to improve the overall writing speed, increase the writing speed, and accelerate the bus frequency. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

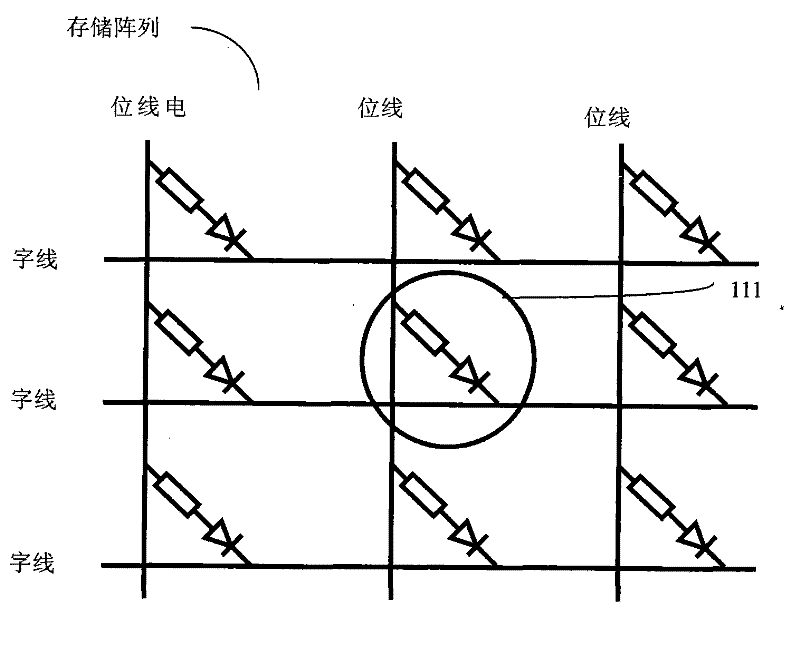

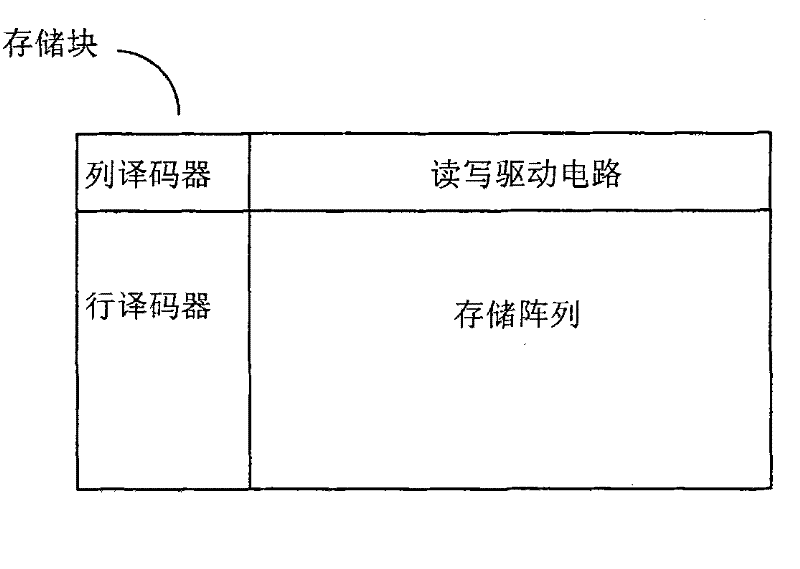

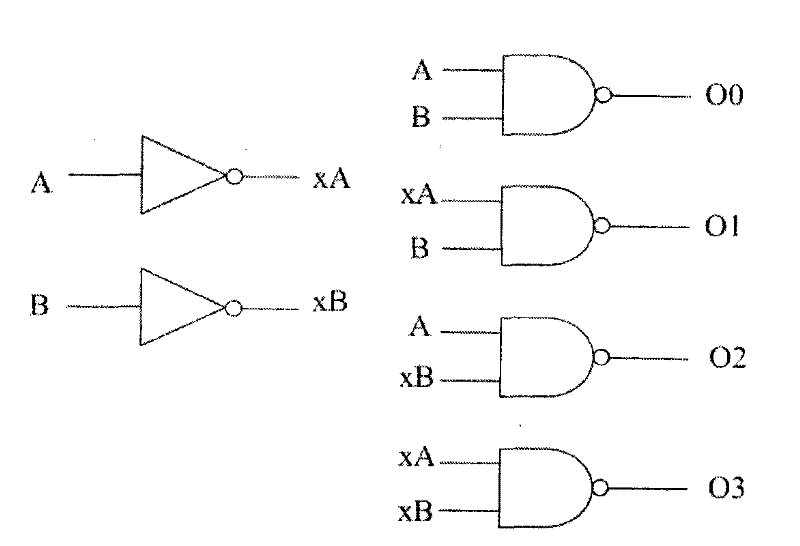

[0038] The invention discloses a phase-change memory, which includes several storage wing planes; the plane includes n storage blocks and n first-in-first-out stack FIFOs, each block corresponds to a FIFO; wherein, n It is a phase change memory to read and write bits in parallel; planes are connected by data bus, address bus and control bus; the data bus transmits write data or read data, the address bus transmits addresses, and the control bus transmits read and write signals. The block includes a storage array, a row and column decoder and a driving circuit. Inside the plane, the FIFO receives read and write signals from the bus.

[0039]When the write signal arrives, the FIFO downloads the data and address to be written from the bus; each FIFO unit stores both the information of the currently written data and the address information of the currently written data; or the FIFO unit only stores the Information about the currently written data. Blocks are written according to...

Embodiment 2

[0071] The present invention proposes a method capable of accelerating the overall burst write speed for the burst write mode of the phase change memory. The so-called burst write method means that a large amount of external data needs to be stored in the memory. In this way, generally, the external bus controller transmits the data to be written to the external bus at a certain frequency, and the memory receives a write command from the external bus, writes data and addresses, and performs a write operation. Due to the huge amount of data, in this method, the speed of writing data alone is usually not considered, but the speed of writing data as a whole is considered, and parallel writing is usually used for multi-bit writing.

[0072] The present invention adopts the following structure to improve the overall writing speed:

[0073] The phase change memory is composed of several storage planes, and each plane is composed of n storage blocks (block) and n first-in-first-out ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More