Element layout capable of increasing layout efficiency and integration degree

A technology of integration and devices, applied in the field of device layout, can solve the problems of reducing layout efficiency, increasing layout design complexity, reducing device integration, etc., to achieve the goal of improving layout efficiency, reducing distance, and increasing integration Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The device layout that can improve the layout efficiency and integration of the present invention will be further described in detail below.

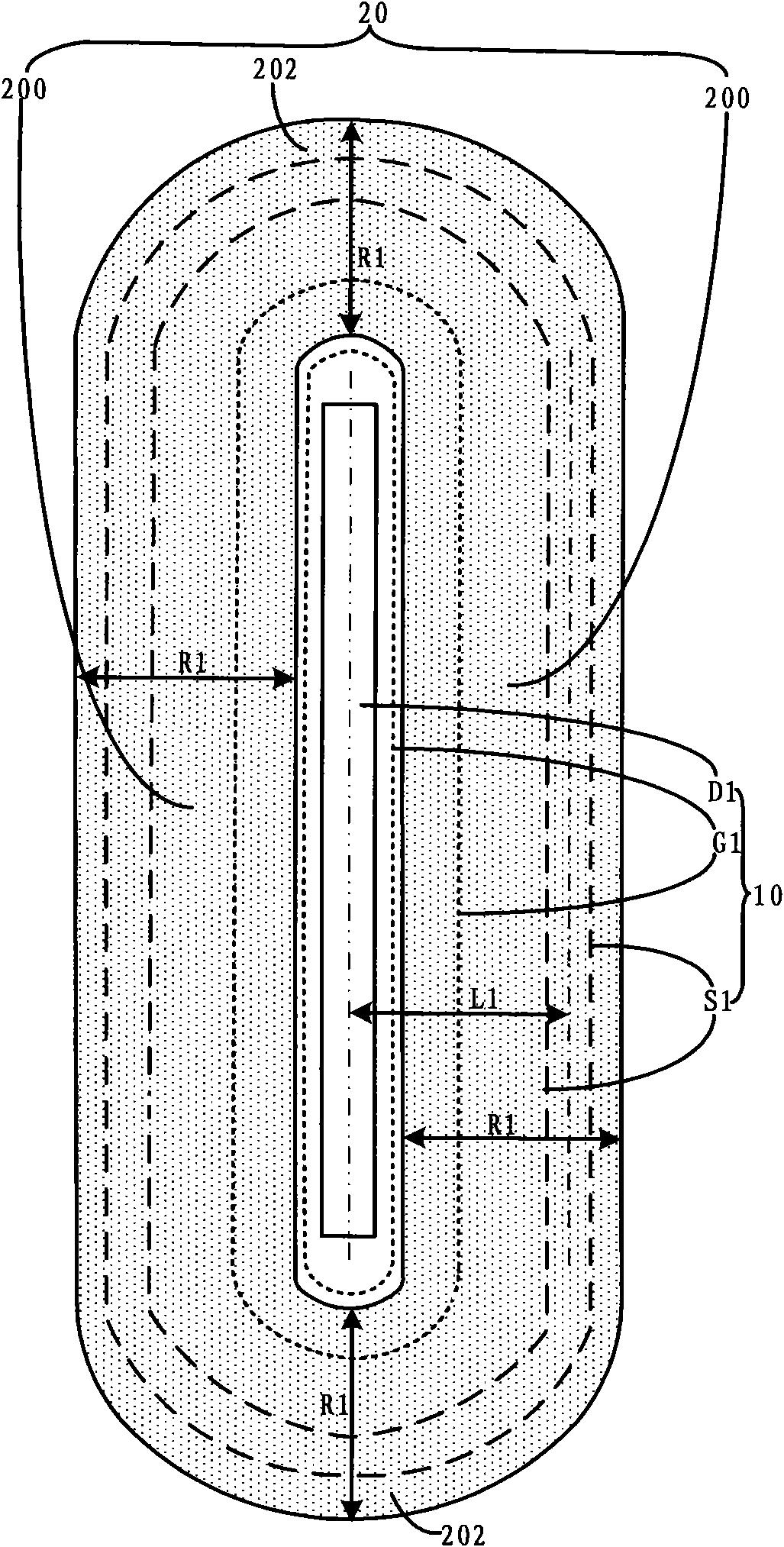

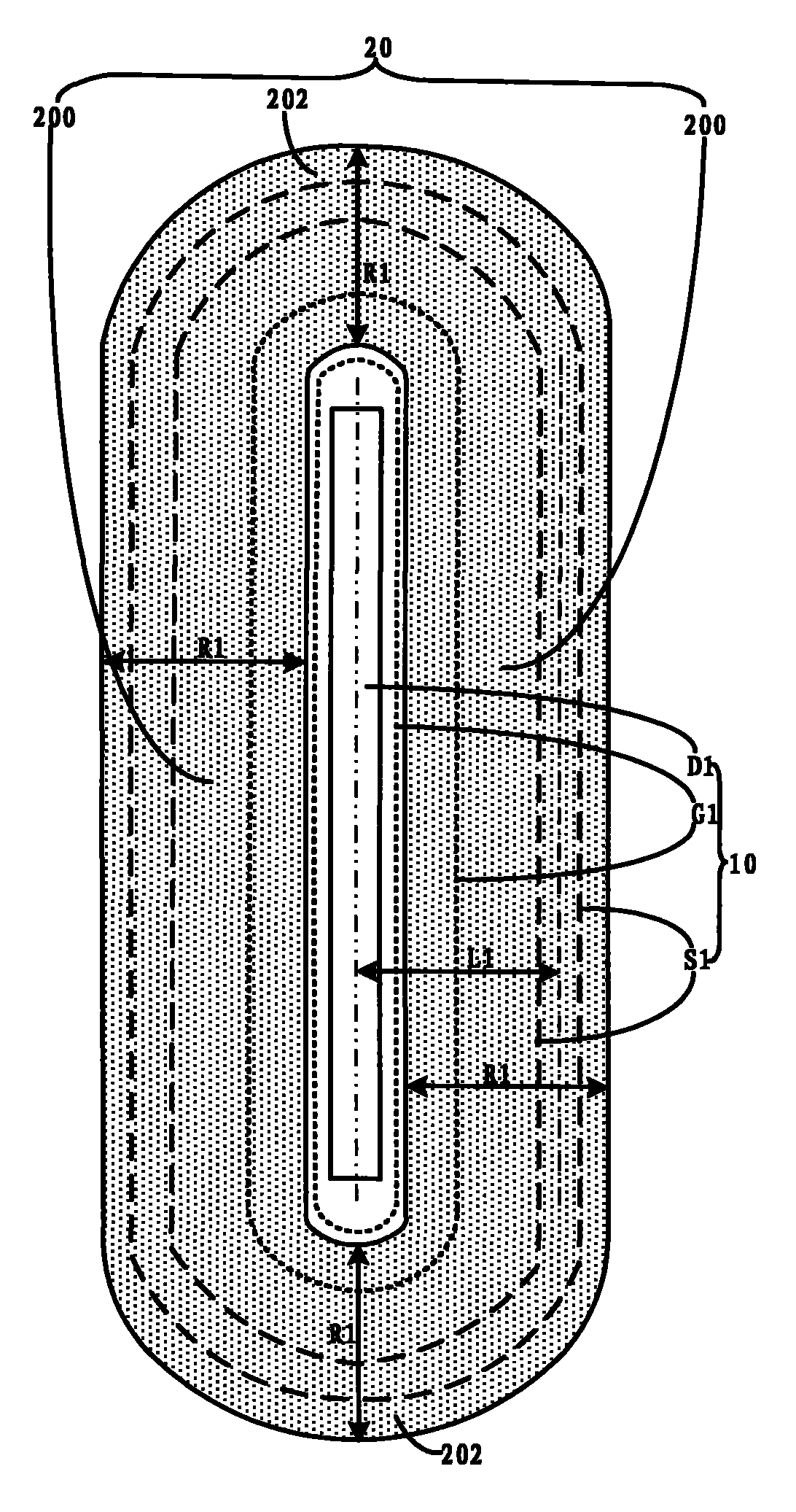

[0017] see figure 1 , which is a schematic diagram of the layout of the first embodiment of the device layout that can improve layout efficiency and integration of the present invention. As shown in the figure, the device layout that can improve layout efficiency and integration of the present invention includes an isolated LDMOS10, The LDMOS10 has a gate G1, a source S1, and a drain D1, and the device layout also includes a first isolation structure 20 surrounding the drain D1, and the ring radius R1 of the first isolation structure 20 is the surrounding drain D1 of the LDMOS10 The distance L1 from the center to the center of the source S1. The first isolation structure 20 includes parallel strips 200 arranged in parallel on both sides of the drain, and an arc-shaped end 202 connected to the end 200 of the parallel strips and f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More