Method for preventing gap below side wall barrier layer during self-aligning silicide process

A self-aligned silicide, barrier layer technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as device leakage, and achieve the effect of preventing gaps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

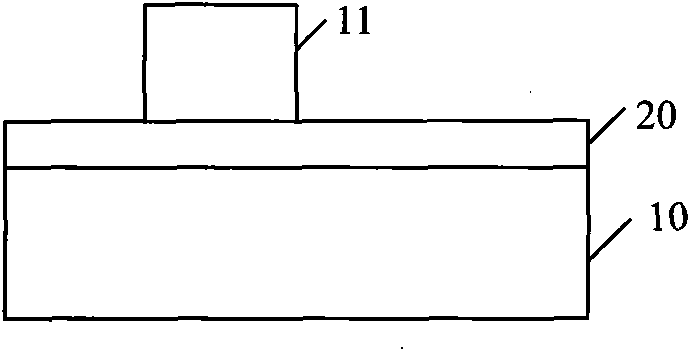

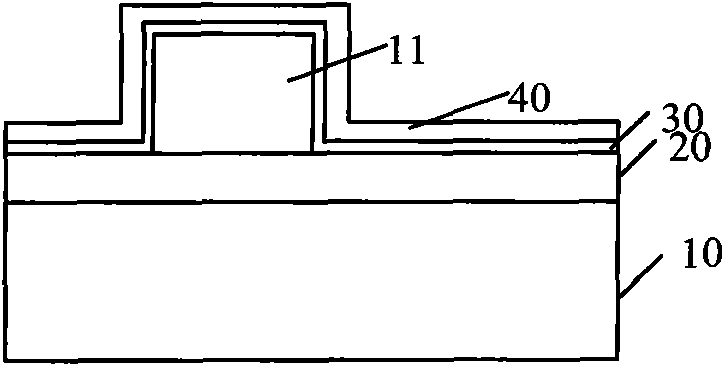

[0054] From figure 2 It can be seen that when the barrier layer of the sidewall of the gate is manufactured by the salicide method, the reason for the gap between the barrier layer, that is, the barrier layer and the device substrate, is: the etching on the device substrate When silicon oxide is used, wet etching is used and due to the relatively thick oxide layer (greater than or equal to 200 angstroms) on the device substrate, the amount of wet etching used is relatively large, resulting in a gap between the barrier layer and the device substrate. The silicon oxide layer is also etched away laterally. Therefore, in order to overcome this defect, the method provided by the present invention first constructs TEOS on the sidewall of the gate to remove ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More