Internal memory interface circuit framework supporting multi-internal memory standard and implementation thereof on metal oxide semiconductor (MOS) process

A technology of circuit structure and process, applied in the fields of logic circuit coupling/interface, logic circuit connection/interface layout, information storage, etc. using field effect transistors, which can solve the problems of chip failure, sharp increase in area, and performance degradation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

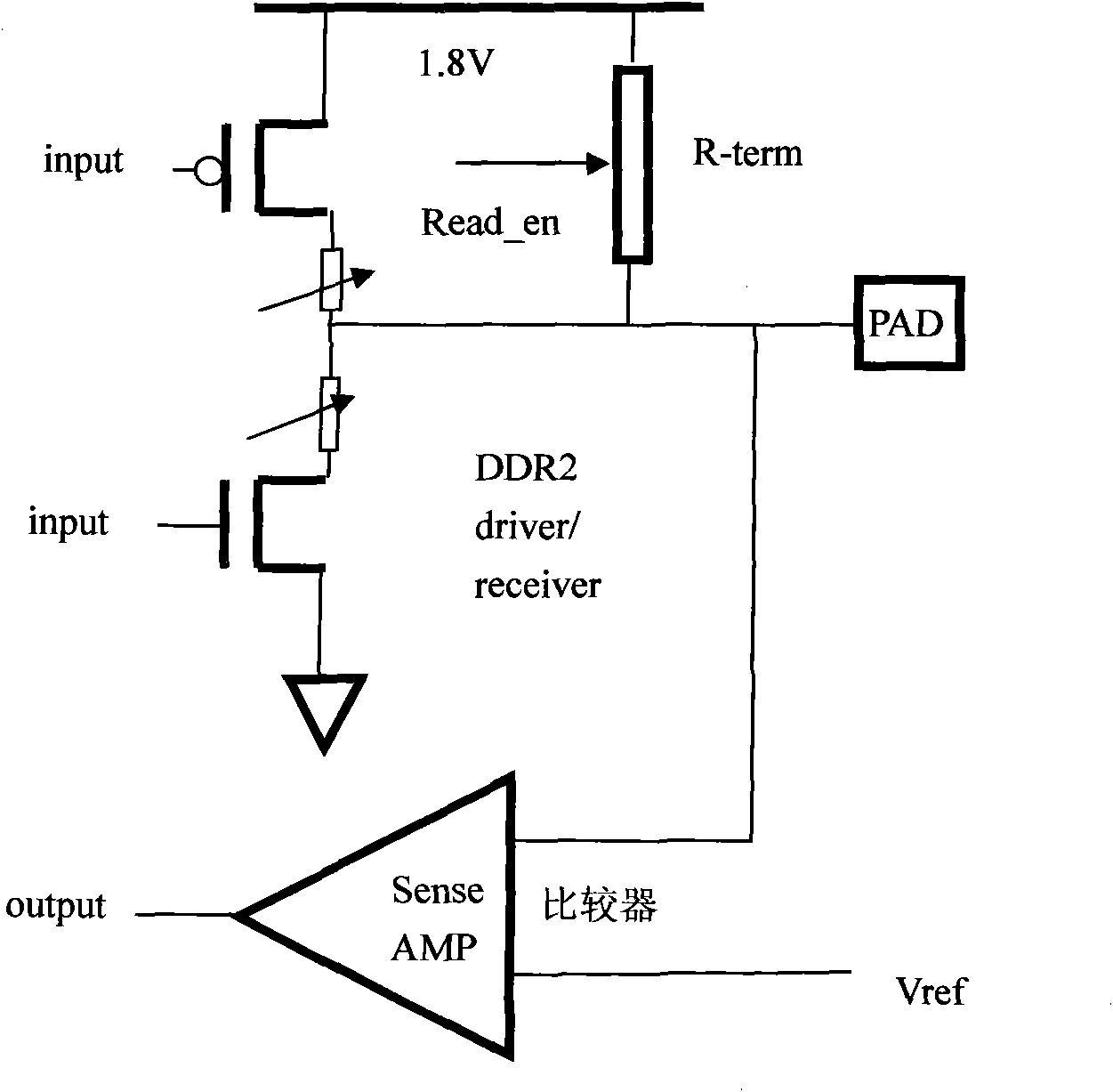

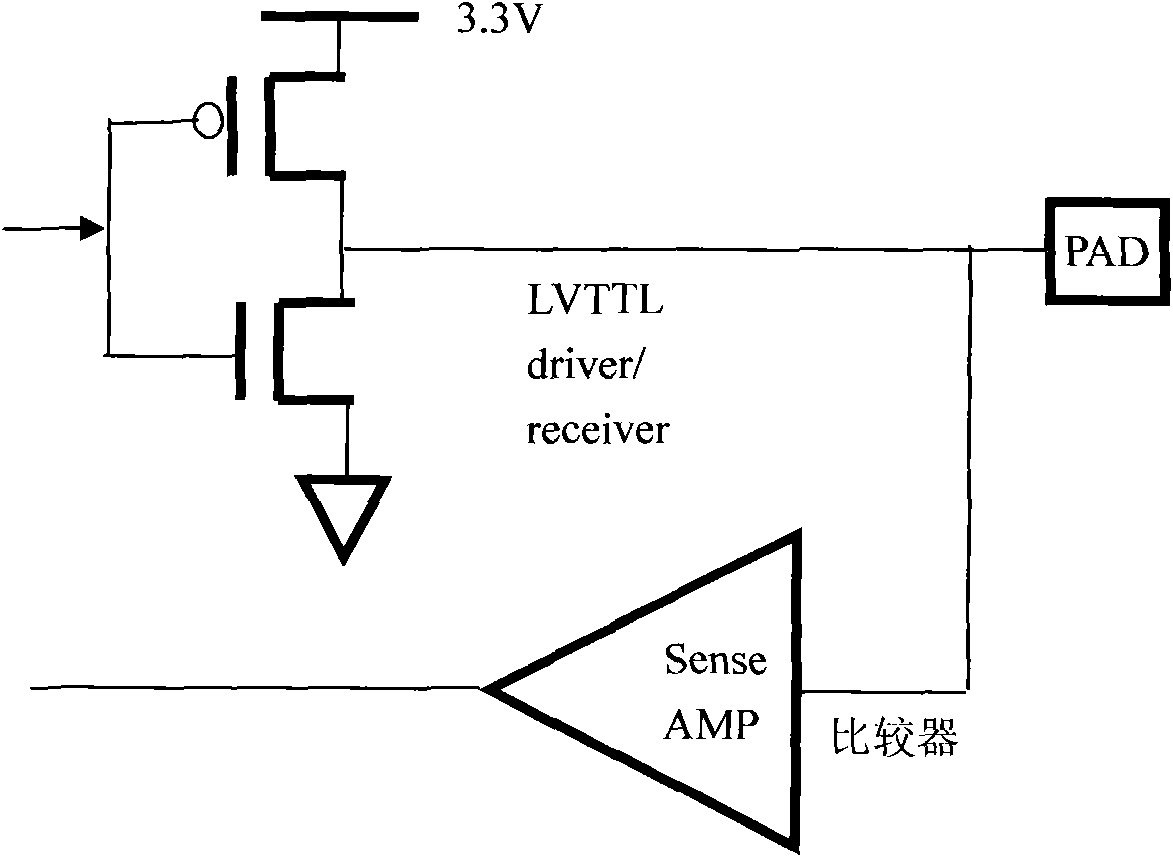

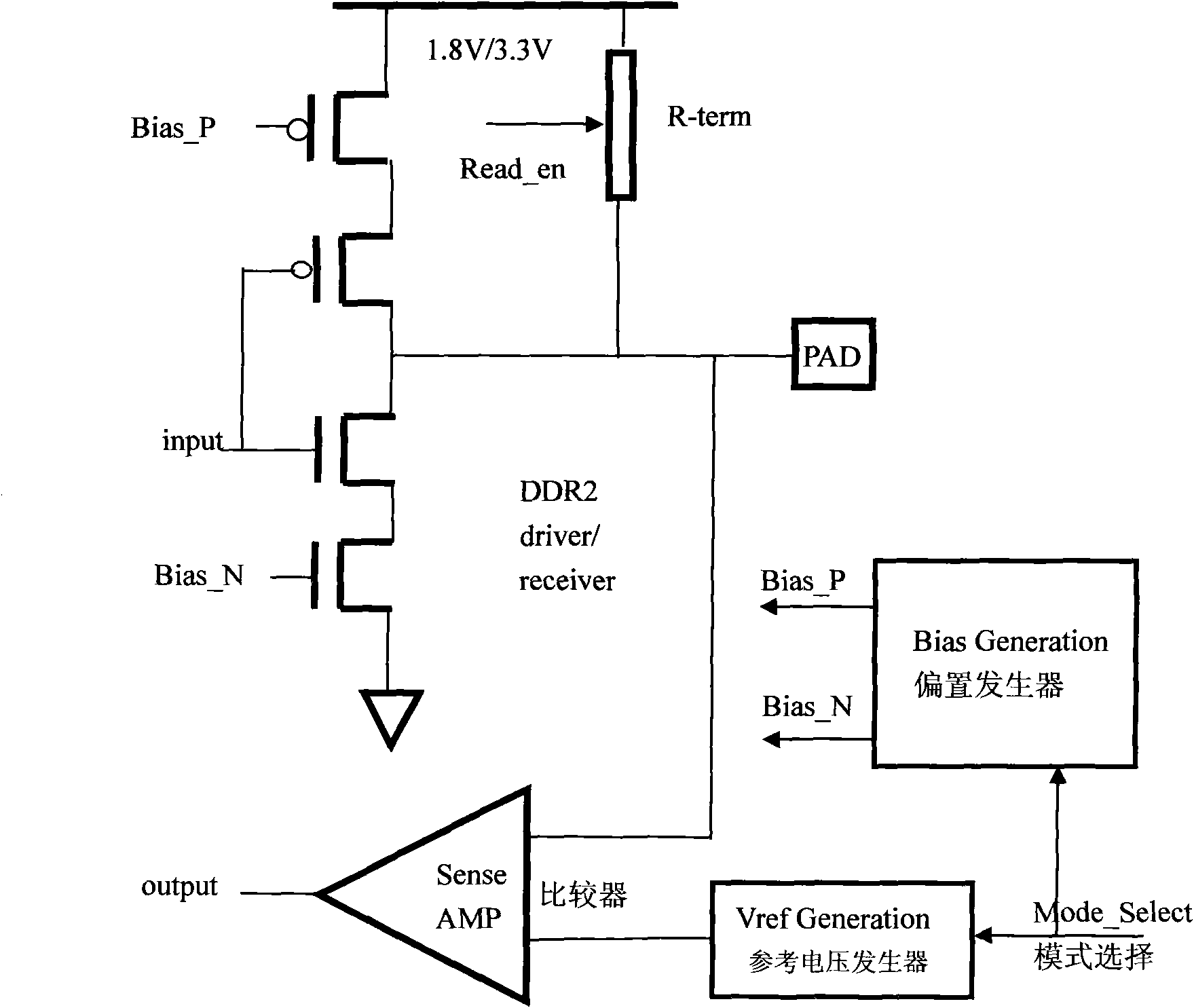

[0011] This patent is implemented in accordance with the content of the third article, and the interface circuit supporting DDR2 or DDR3 is modified. The specific implementation can be carried out according to Figure 4 , 5 , 6 instructions, so that the interface circuit to achieve the purpose of supporting 4 different memory standards. After the transformation is completed, select the power supply voltage according to the different memory standards supported. For example, if it is SDR SDRAM, use 3.3V power supply voltage, and if mobile SDRAM, DDR2, and mobile DDR use 1.8V voltage. A four-to-one selection circuit is added to the input and output ends of the interface, and the interface is controlled through the mode selection signal to make it work normally.

[0012] The area and power consumption of the memory interface described in this patent are increased by about 30% on the basis of only supporting DDR2 interface circuits, and the simple solution of stacking circuits of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com