Digital delay phase locked loop circuit

A delay phase locked loop, digital delay line technology, applied in the direction of electrical components, automatic power control, etc., can solve the problem of slow locking speed, narrow applicable frequency, etc., to solve the problem of false lock, wide frequency range, and solve the problem of slow locking speed. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

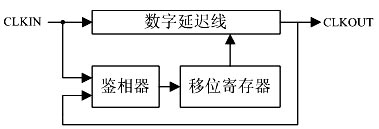

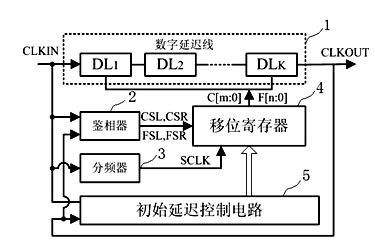

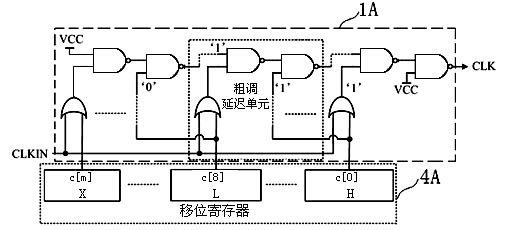

[0021] figure 2 is a digital delay-locked loop structure diagram, which is an improved register-controlled digital delay-locked loop, and the structure includes five functional modules: digital delay line 1, phase detector 2, clock divider 3, improved shifter Bit register 4, initial delay control circuit 5. The digital delay line 1 is composed of K (K is a natural number) identical delay units, each delay unit is controlled by the output signal of the improved shift register 4, and the phase detector 2 compares the input clock CLKIN with the delayed output clock CLKOUT Phase, before reaching a stable state, control the improved shift register 4 to shift left or right according to the phase comparison result, and the initial delay control circuit 5 measures the delay time from the input clock CLKIN to the output clock CLKOUT when starting up (using the input clock period The number indicates), so as to measure the initial condition of the system work, and then generate a set ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More