Steady-state thermal analysis method of stack type three-dimensional FPGA (Field Programmable Gate Array) chip

A thermal analysis, stacked technology, used in special data processing applications, instruments, electrical digital data processing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0091] The solutions of the present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

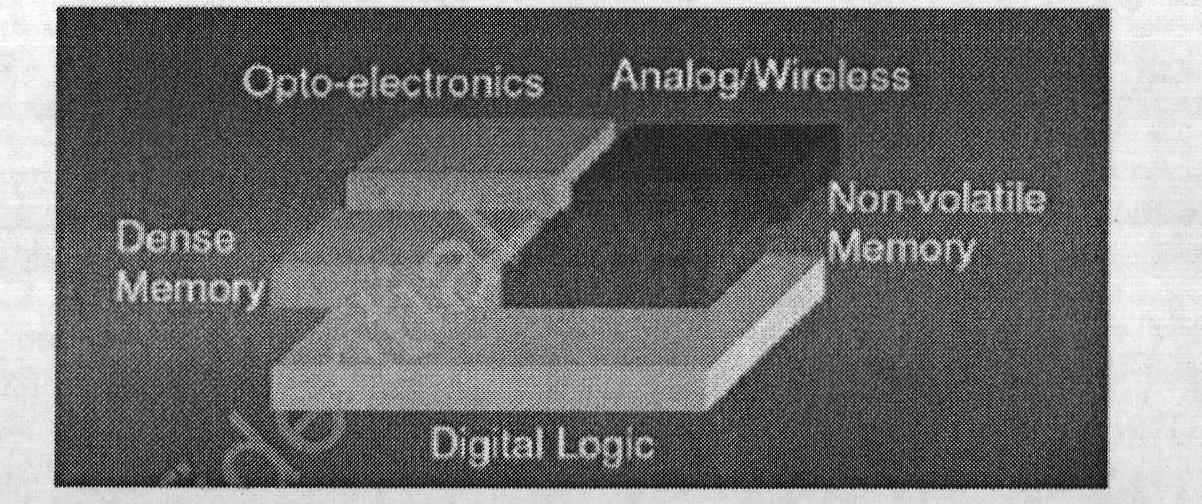

[0092] Figure 15 It is a stacked chip design including two FPGA chips. B represents the contact point between chip 1 and chip 2, and X represents the internal point of chip 1. Define B’ and Y in the same way. It can be seen that B and B' represent the same point in this stacked chip structure, but in order to simplify the analysis, we regard B and B' as different points, and B and B' are connected by a one-dimensional superconductor, we This hypothetical structure of high thermal conductivity is called a virtual element.

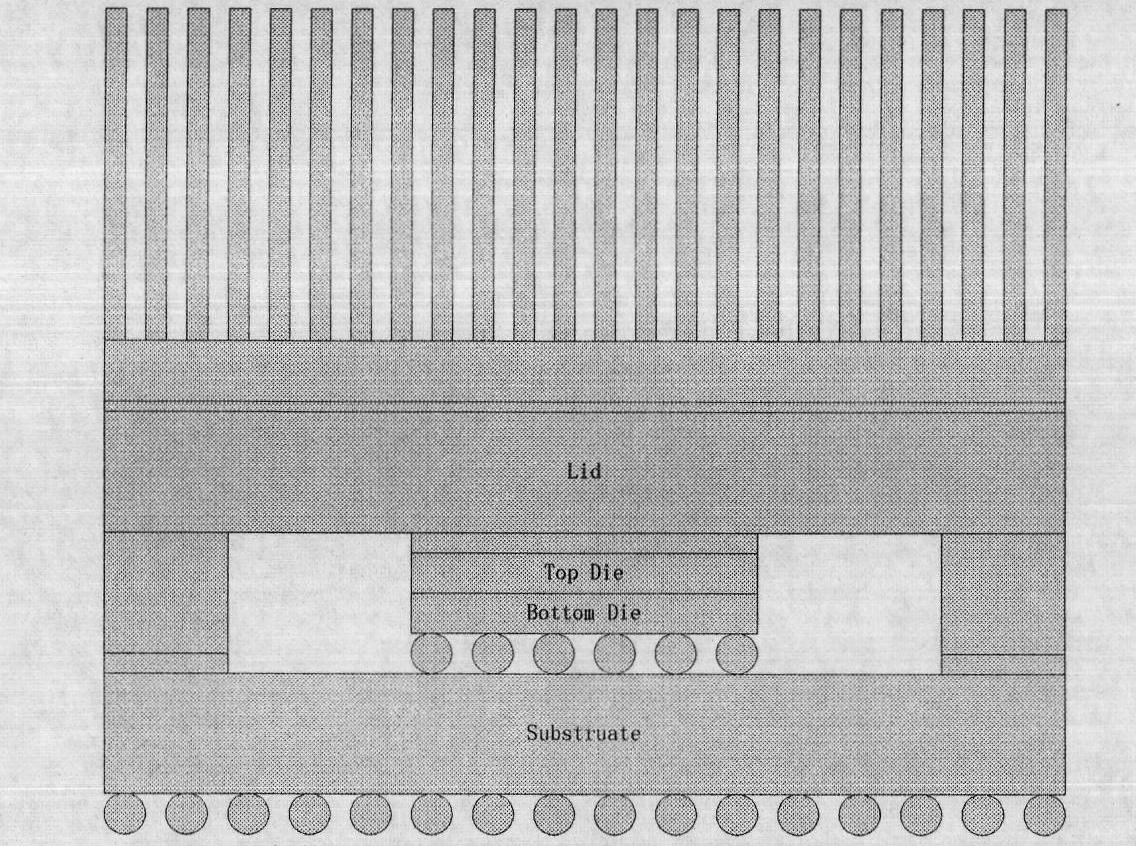

[0093] Figure 16 is a flow chart of the stacked three-dimensional FPGA chip thermal analysis algorithm, [K i ] is the heat conduction matrix of chip i, in the following we will analyze the structure of the matrix [K] in detail, and how the preprocessing matrix is established.

[0094] The thermal cond...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More