Transistor structure with etch stop layer and manufacturing method thereof

An etch stop layer and etch stop technology, which is applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problem of uneven electrical properties of transistors and achieve good reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

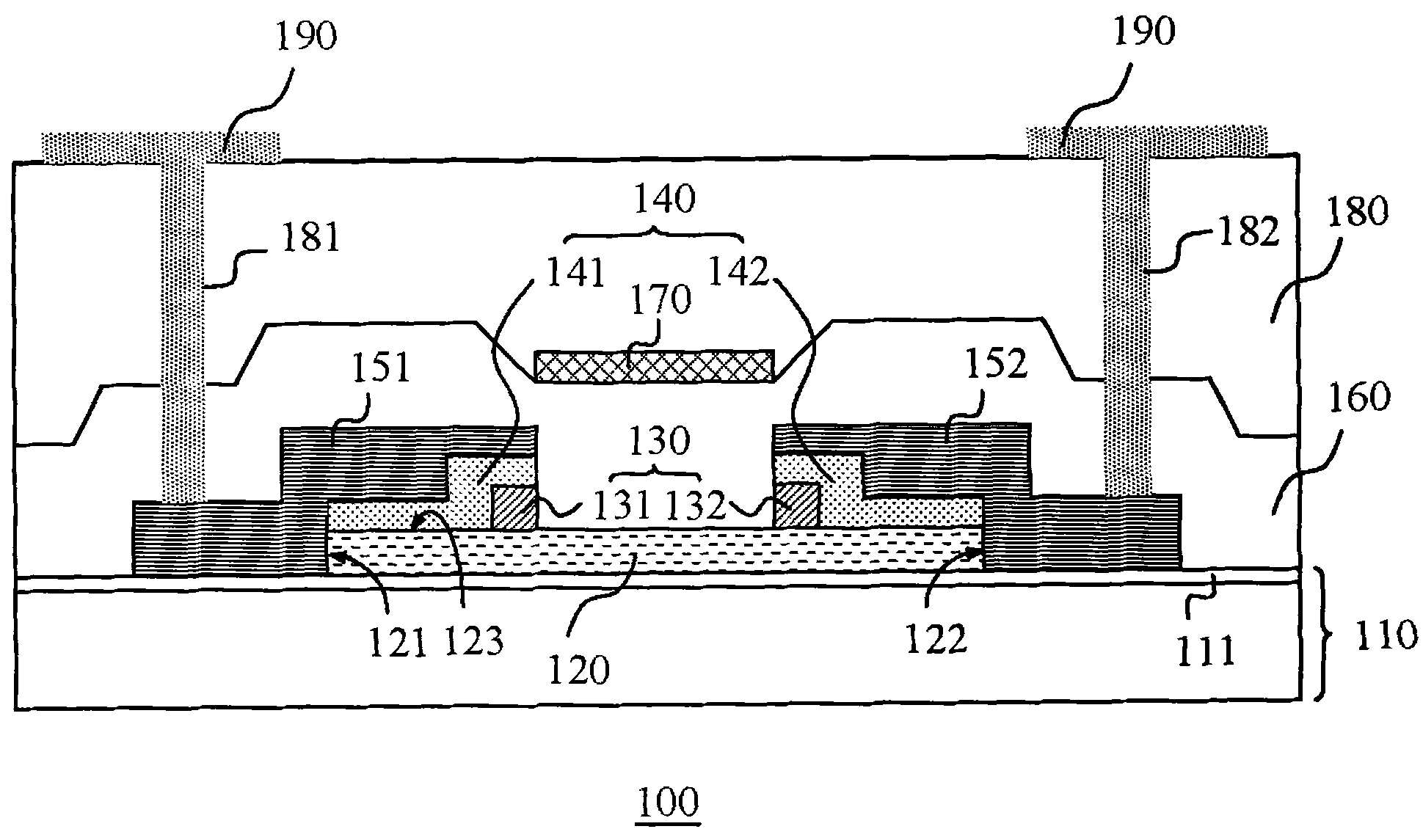

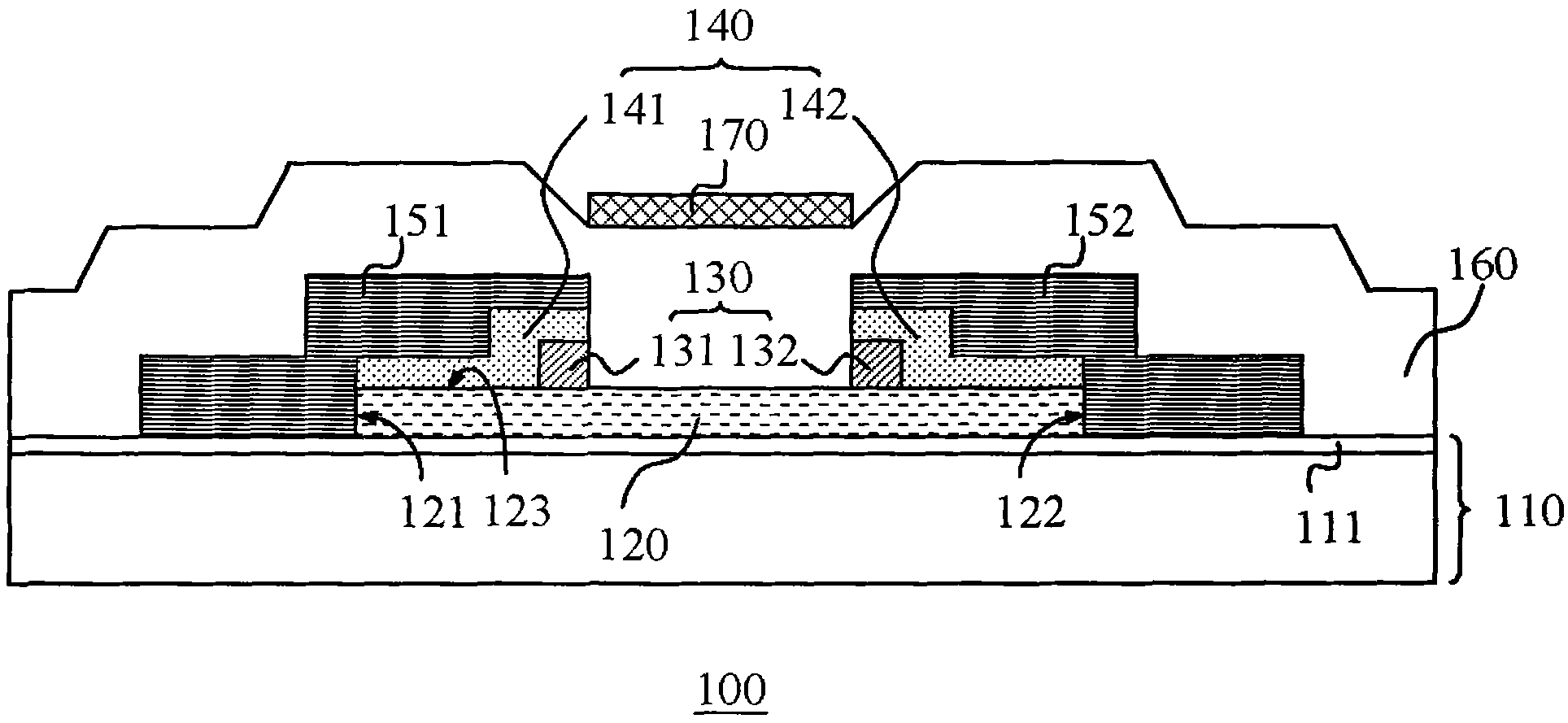

[0053] Next, with the reference Figure 2A , 2B , respectively depict schematic diagrams of Embodiments 1 and 2 of the main characteristic structure of the transistor of the present invention. Such as Figure 2A In the first embodiment shown, the first part 131 of the etch stop structure 130 is sandwiched between the first ohmic contact region 141 and the crystalline semiconductor layer 120, and the second part 132 of the etch stop structure 130 is sandwiched between the first ohmic contact region 141 and the second crystalline semiconductor layer 120. Directly below the two ohmic contact regions 142 and between the crystalline semiconductor layer 120 , and the first portion 131 and the second portion 132 of the etch stop structure 130 are not in contact. therefore, figure 1 In the transistor structure 100 , the etch stop structure 130 exposes the partially crystalline semiconductor layer 120 .

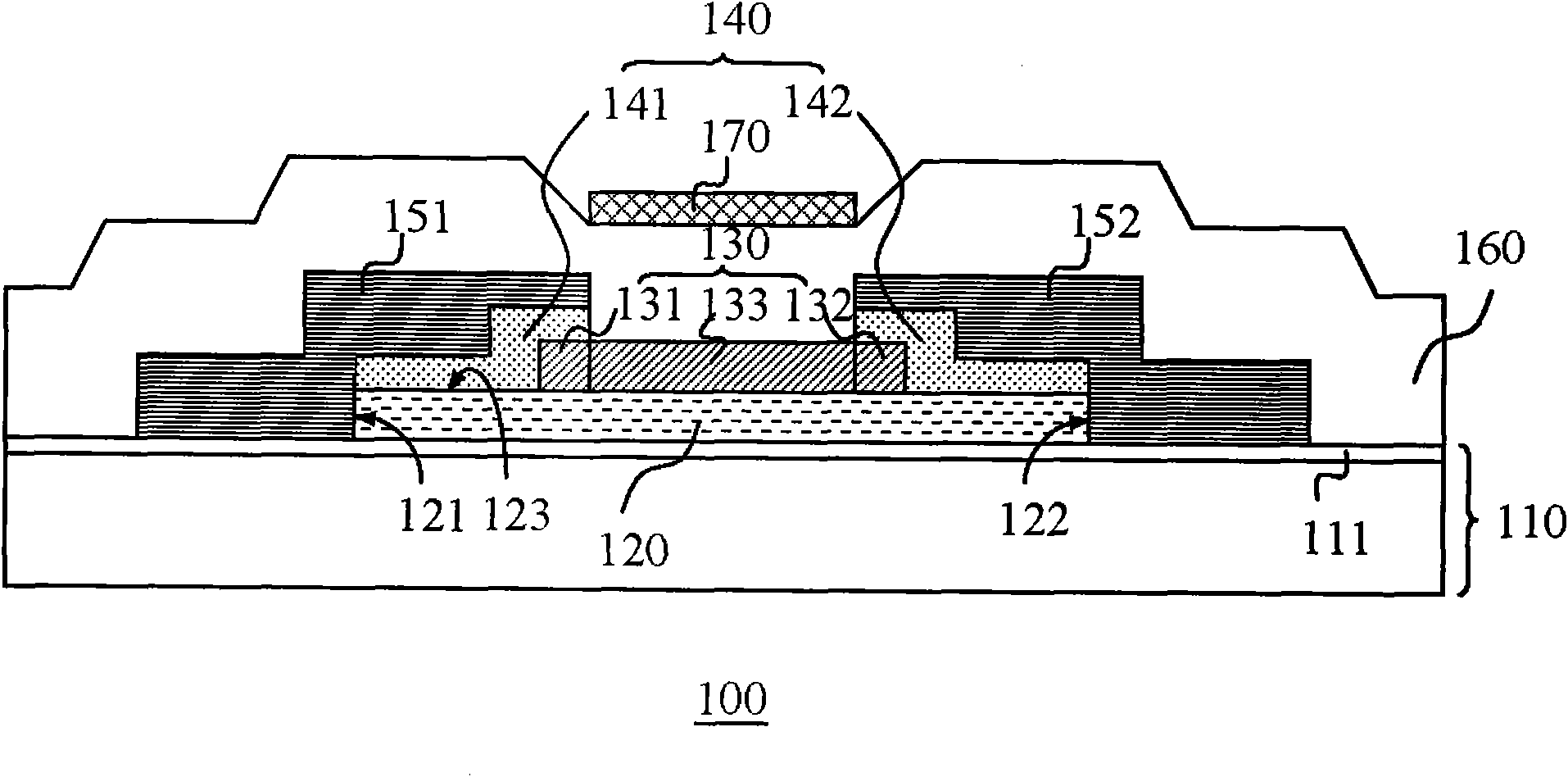

[0054] Also, if Figure 2B In the second embodiment shown, except for the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More