Built-in system test method of multiple static random access memory (SRAM) based on scanning test

A built-in self-test and scan test technology, which is applied in the field of integrated circuit design, can solve the problems of not being applicable to multiple SRAM designs and low test coverage, so as to save scan test vectors, save scan test time, and save scan test time Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

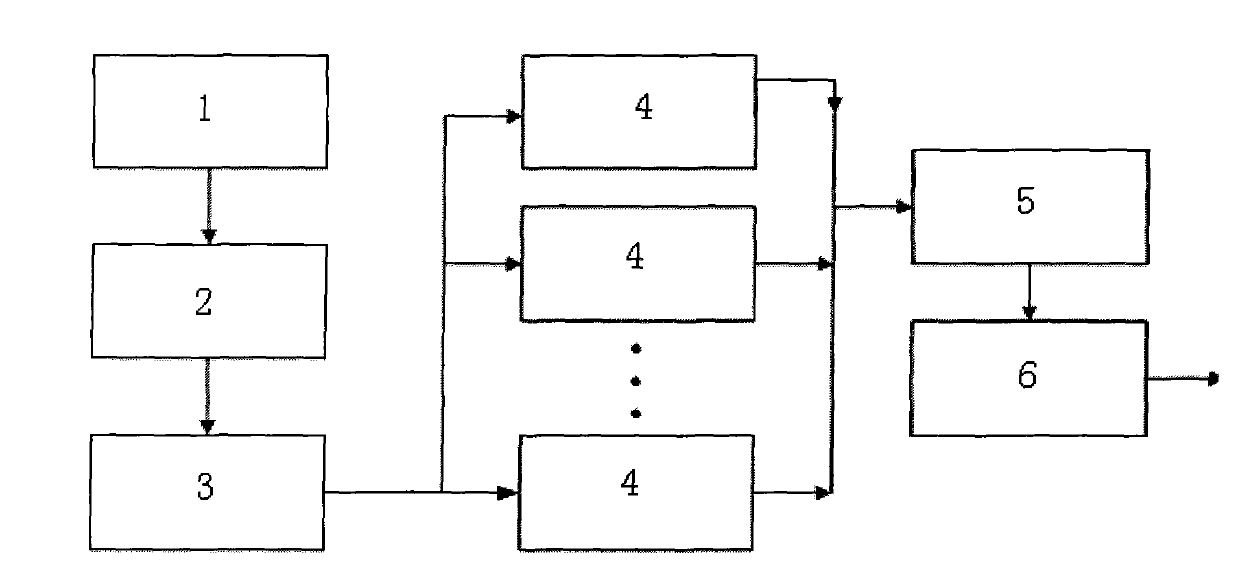

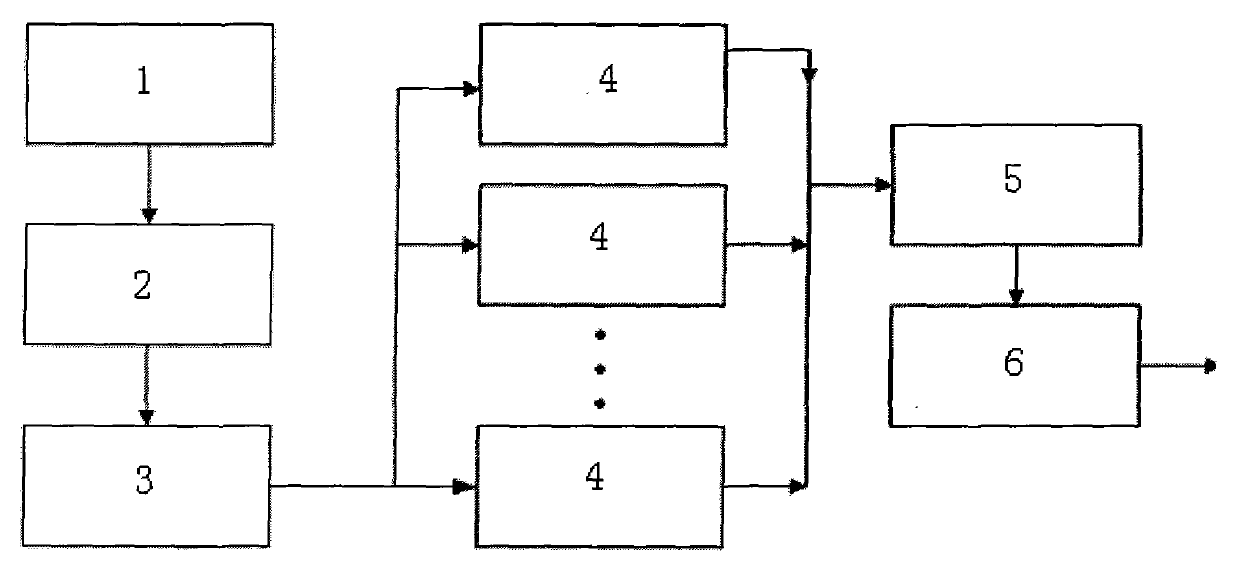

[0031] A built-in self-test method for multiple SRAMs based on scan testing, such as figure 1 As shown, the system-on-chip with multiple SRAM cores is tested internally. The system-on-chip includes input pins and output pins. The test vector generation module 1, the control module 2 and the input encoding and decoding module 3 are sequentially connected and then connected. To the input pin of the system on chip; the output pin of the system on chip is connected with the output codec module 5 and the result output module 6 in sequence; the result output module 6 is connected with the oscilloscope, and the specific steps of the method are as follows:

[0032] (1) For multiple SRAM resources, create two modes, namely scan mode and built-in self-test mode; create mode signal test_mode: when the test_mode signal is "01", the system enters scan mode; when the test_mode signal is "10" , the system enters the built-in self-test mode;

[0033] (2) When multiple SRAMs are in scan mode,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More