Forming method of through hole

A via-hole and patterning technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., to save process operation time, save costs, and reduce standing wave effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0056] The method for forming the via hole in this embodiment includes:

[0057] Firstly, a substrate is provided, and a dielectric layer is provided on the substrate;

[0058] Secondly, coating a photoresist layer on the dielectric layer;

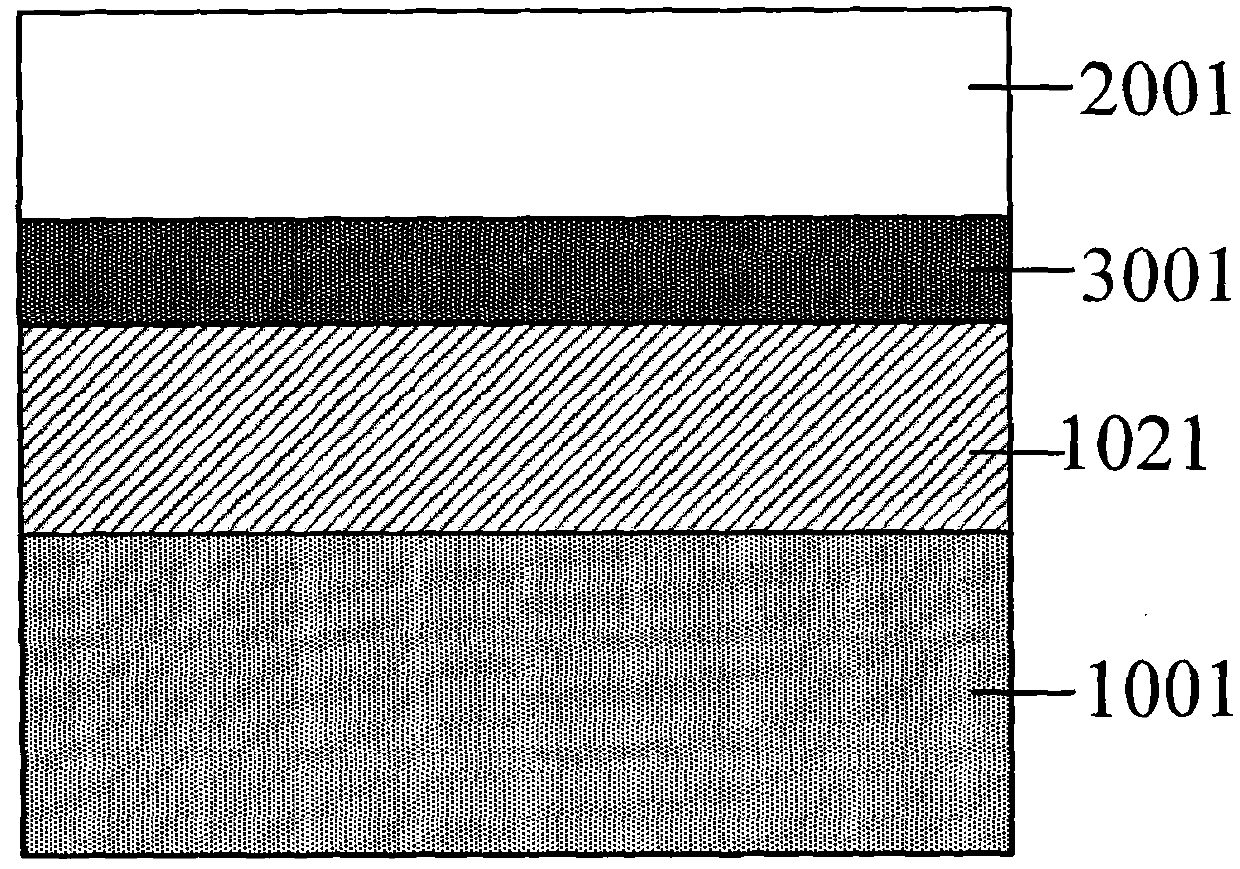

[0059] Figure 2A Shown is a schematic cross-sectional view of the substrate after coating the photoresist layer on the substrate, as Figure 2A As shown, there is a dielectric layer 102 on the substrate 100, and a photoresist layer 200 is coated on the dielectric layer 102;

[0060] Preferably, a dye is added into the photoresist layer, and the dye can reduce light interference;

[0061] Preferably, it also includes: performing post-baking (PEB, Post Exposure Baking) and hard-baking (HB, Hard Baking) on the photoresist layer to reduce the standing wave effect;

[0062] Secondly, patterning the photoresist layer by exposure;

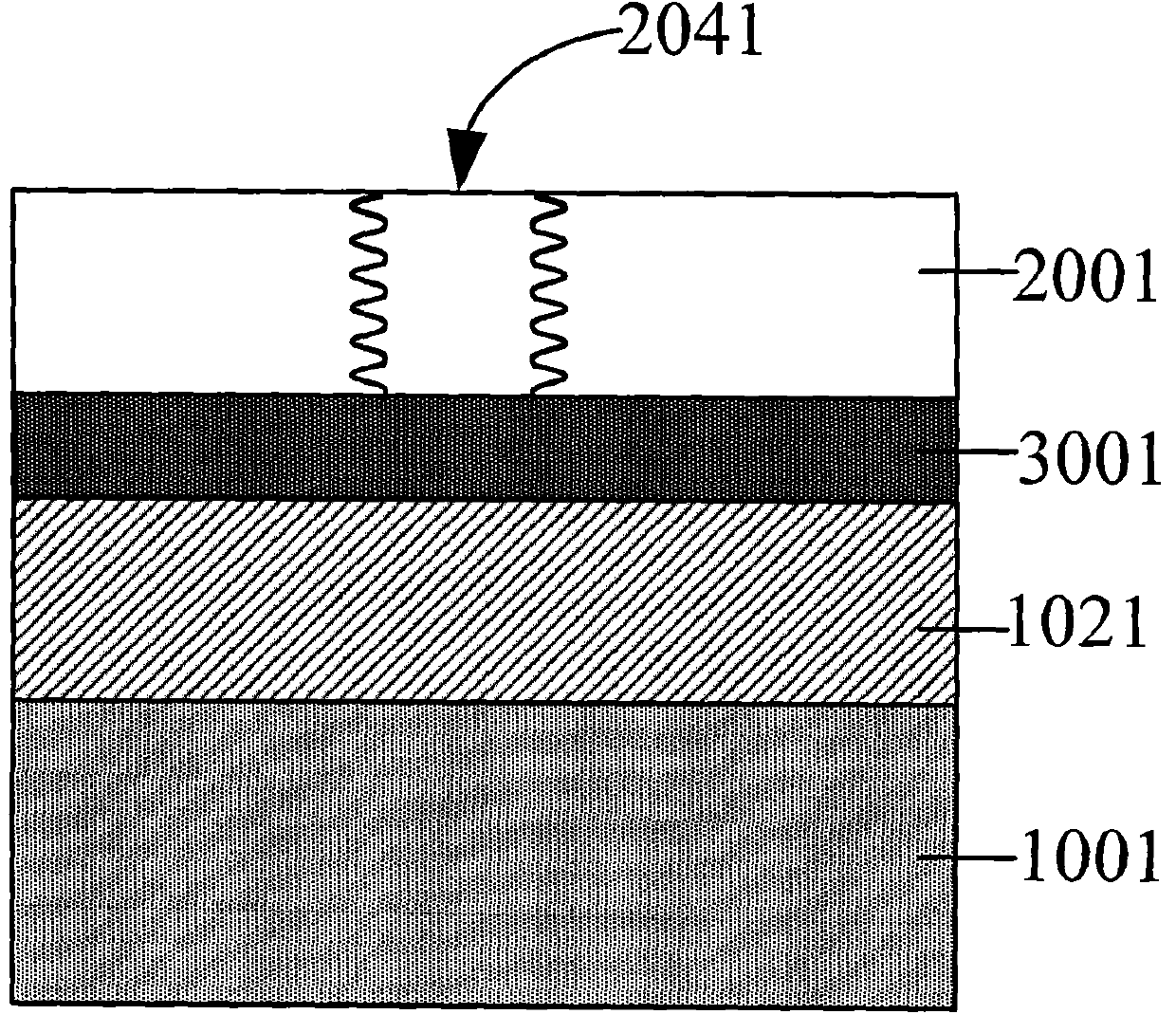

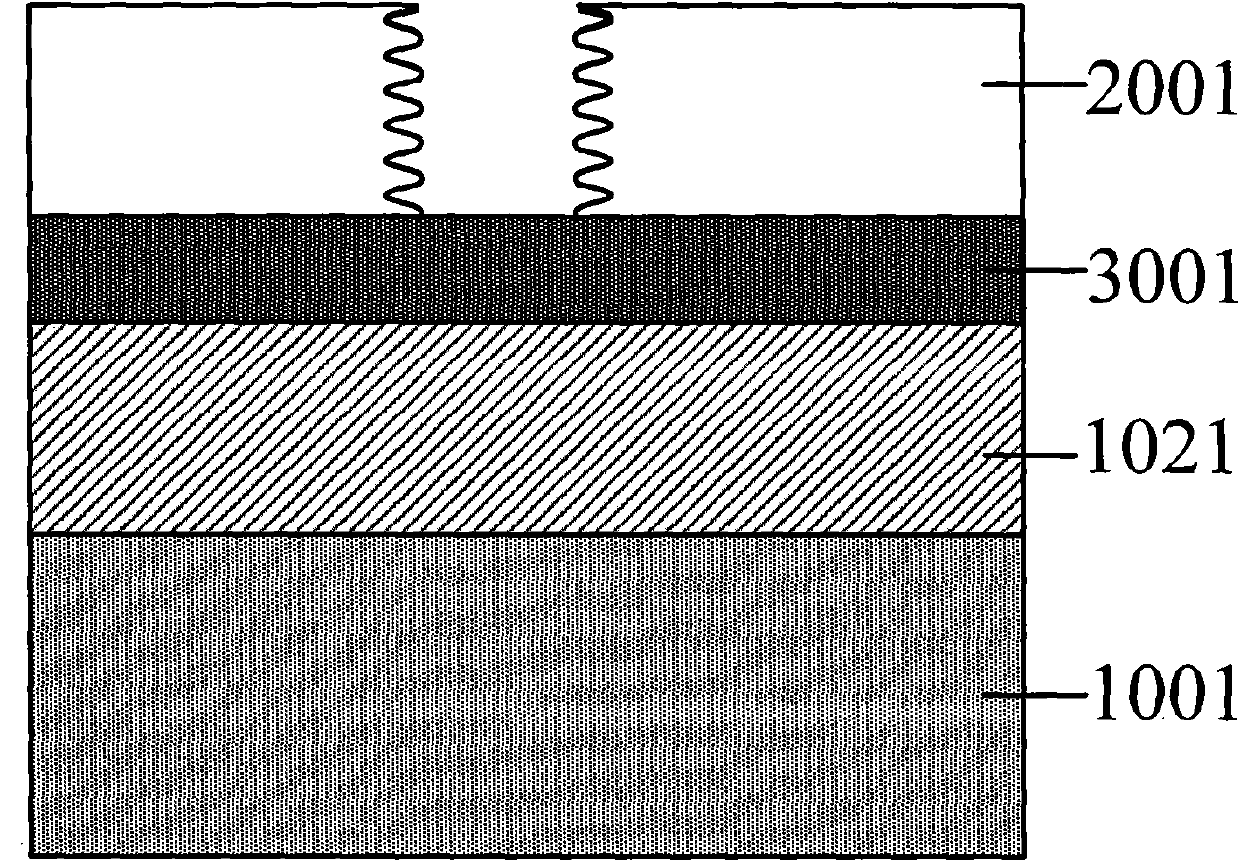

[0063] Figure 2B It is a schematic cross-sectional view of the substrate after exposing the photoresist, su...

Embodiment 2

[0079] Figure 3F It is a flow chart of a method for forming a via hole in an embodiment, referring to Figure 3F As shown, the method for forming the via hole in this embodiment is described in detail, including:

[0080] Firstly, a substrate is provided, on which a dielectric layer and a bottom anti-reflection layer are sequentially arranged;

[0081] The bottom antireflective coating (BARC, Bottom Anti-Reflective Coating) is located at the bottom of the photoresist layer, and is used to reduce the reflection of light at the bottom of the photoresist layer; the material of the bottom antireflective layer can be an organic antireflective coating ( Organic), which is formed by spin coating, and the organic reflective coating can directly receive the incident light; the material of the bottom antireflective layer can also be an inorganic antireflective coating (Inorganic), which uses plasma enhanced chemical vapor phase Formed by deposition (PECVD, Plasma Enhanced Chemical Va...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More