Programmable digital frequency multiplier

A frequency multiplier and frequency multiplication technology, applied in the direction of power oscillators, electrical components, etc., can solve the problems of increased volume, low frequency and phase tracking accuracy, complex frequency control algorithm, etc., to ensure zero error output and anti-interference The effect of ability improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Below in conjunction with accompanying drawing, preferred specific embodiment of the present invention is described:

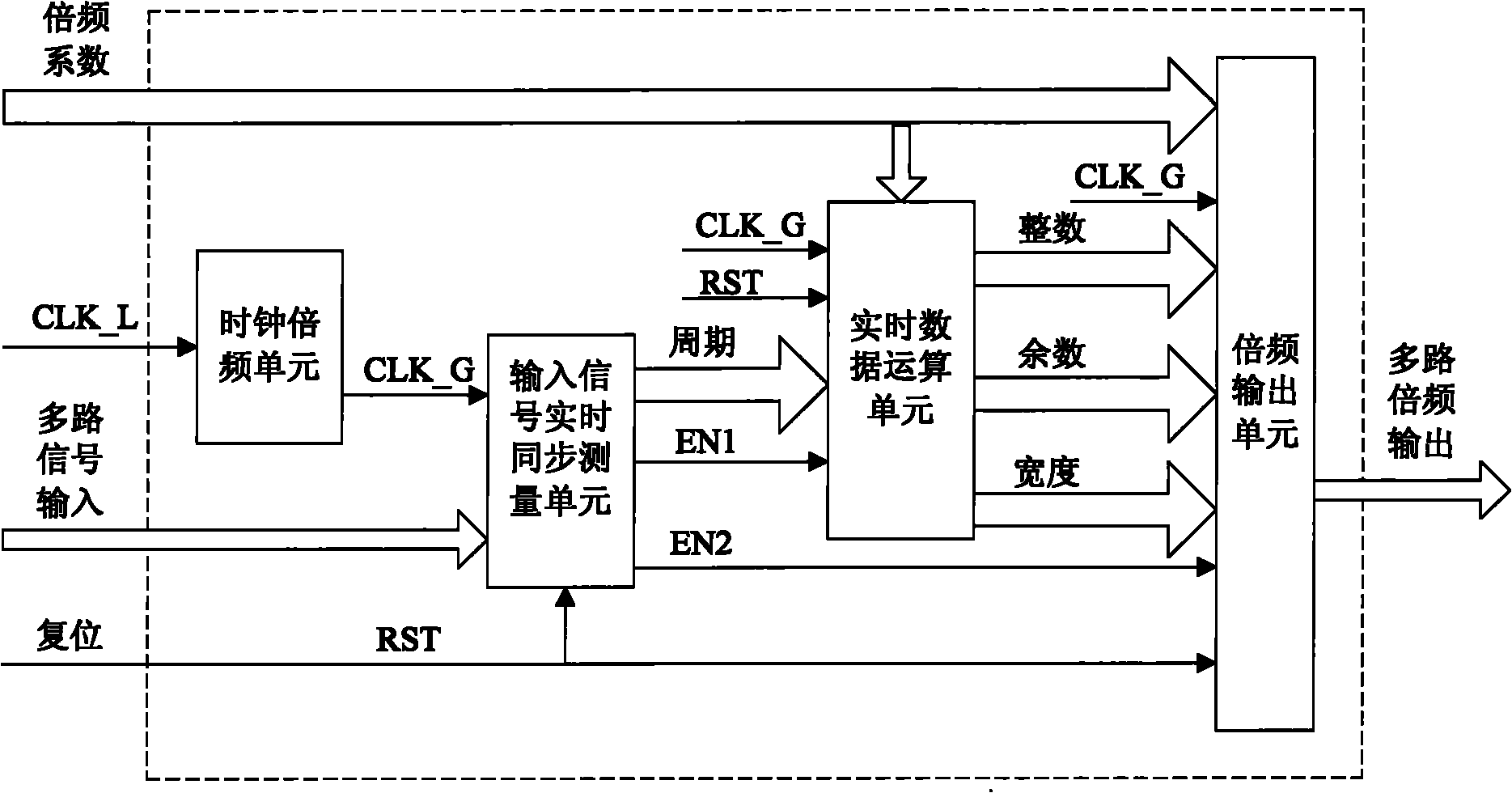

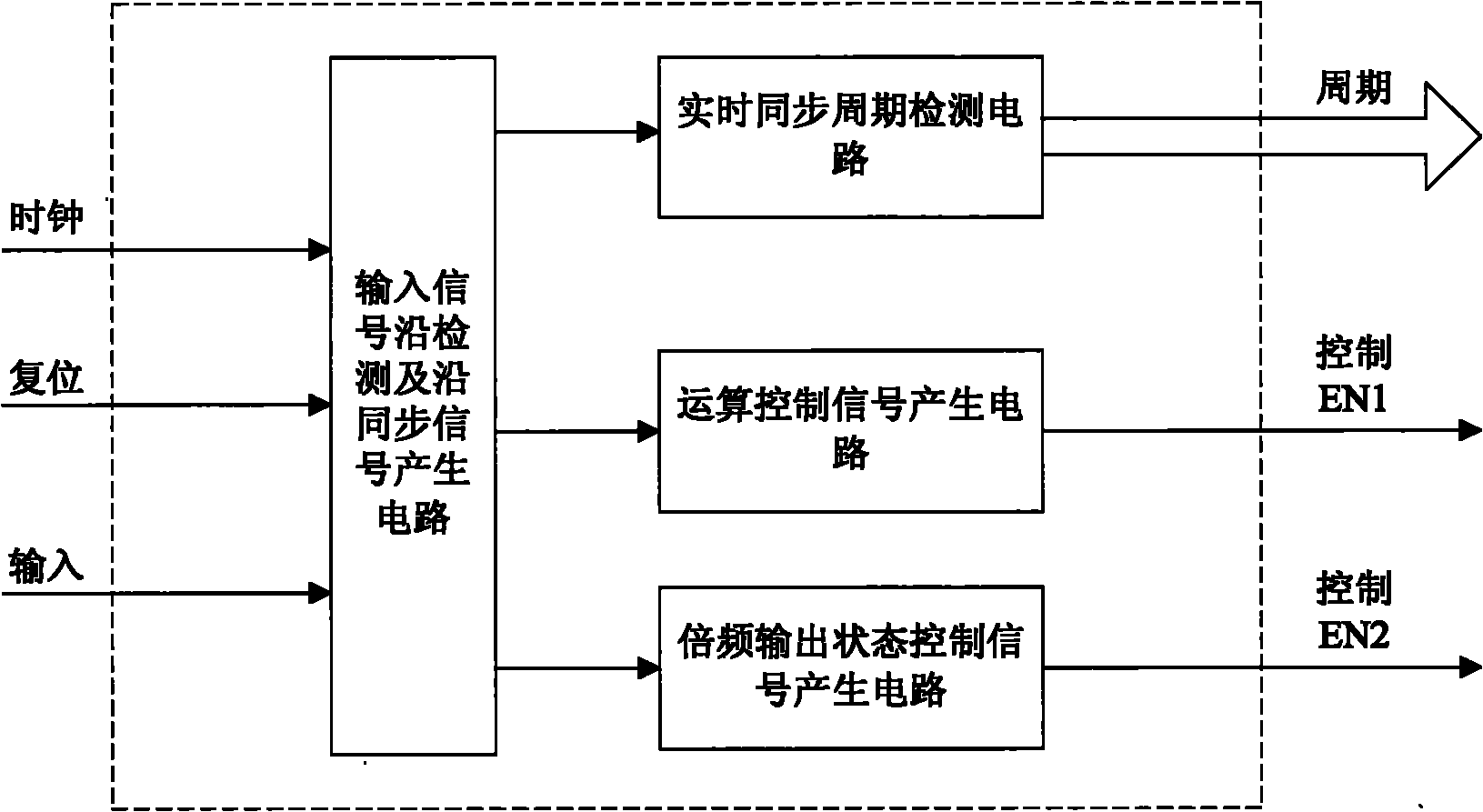

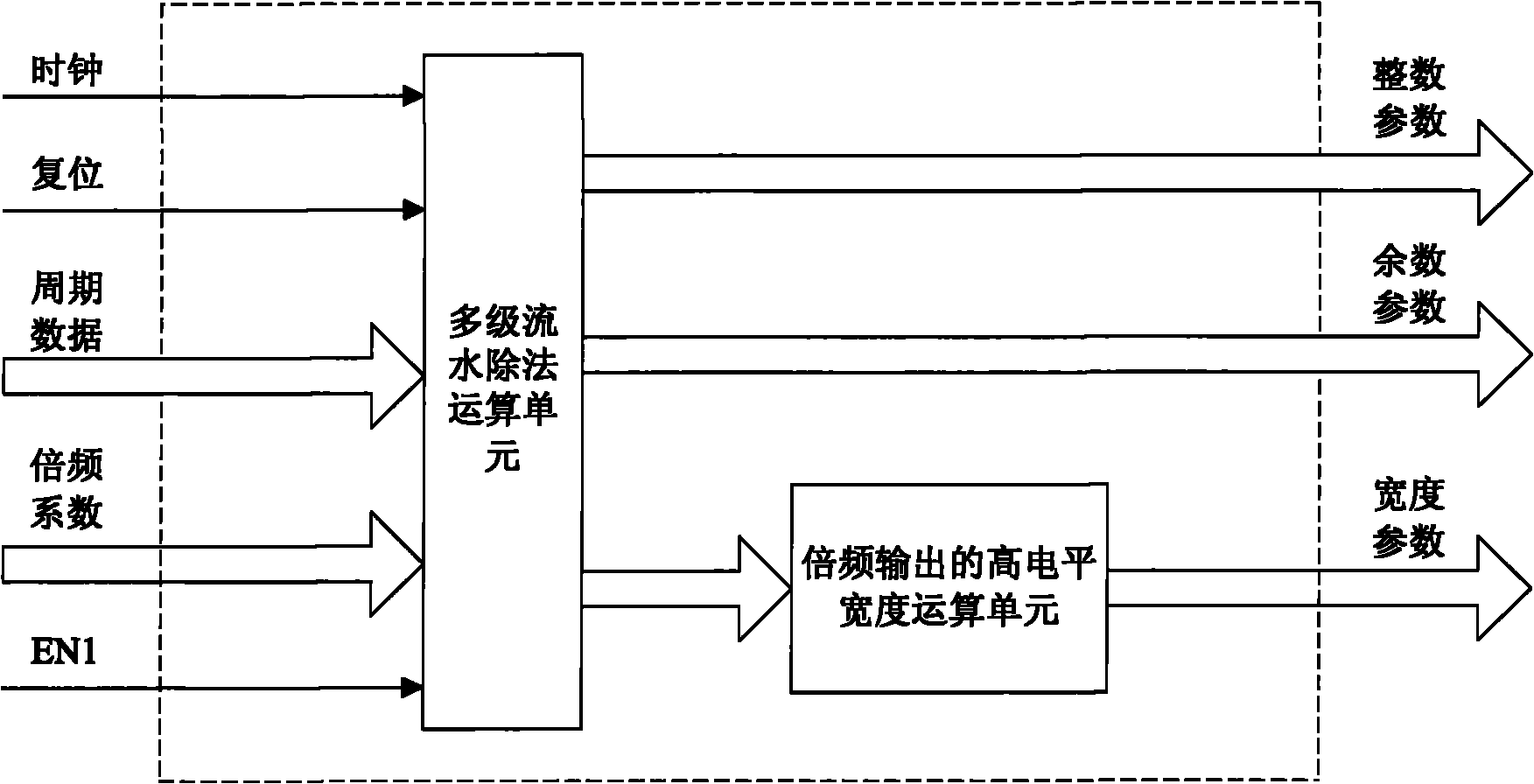

[0027] Such as figure 1 The frequency multiplier shown is mainly composed of clock frequency multiplication unit, input signal real-time synchronous measurement unit, real-time data calculation unit, frequency multiplication output unit and other module units. Each functional unit is realized by digital circuit, which can be packaged in a On the chip, as shown by the dotted line in the figure, some input and output pins are arranged on the periphery of the chip. In the present invention, the input pins include the input of the frequency multiplication coefficient, the input of the system low-frequency clock CLK_L, the input of the input signal to be multiplied and the reset Signals, etc., the output pins only show the multiplier signal output in the attached figure. The following will introduce each functional unit in detail:

[0028] The clock frequen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More