Clock phase-splitting technology-based precise digital time delay synchronous machine and time delay method

A technology of digital delay and synchronous machine, applied in the direction of pulse technology, single output arrangement, pulse processing, etc., can solve the problems of complex phase detection and phase compensation circuits, and achieve the effect of low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

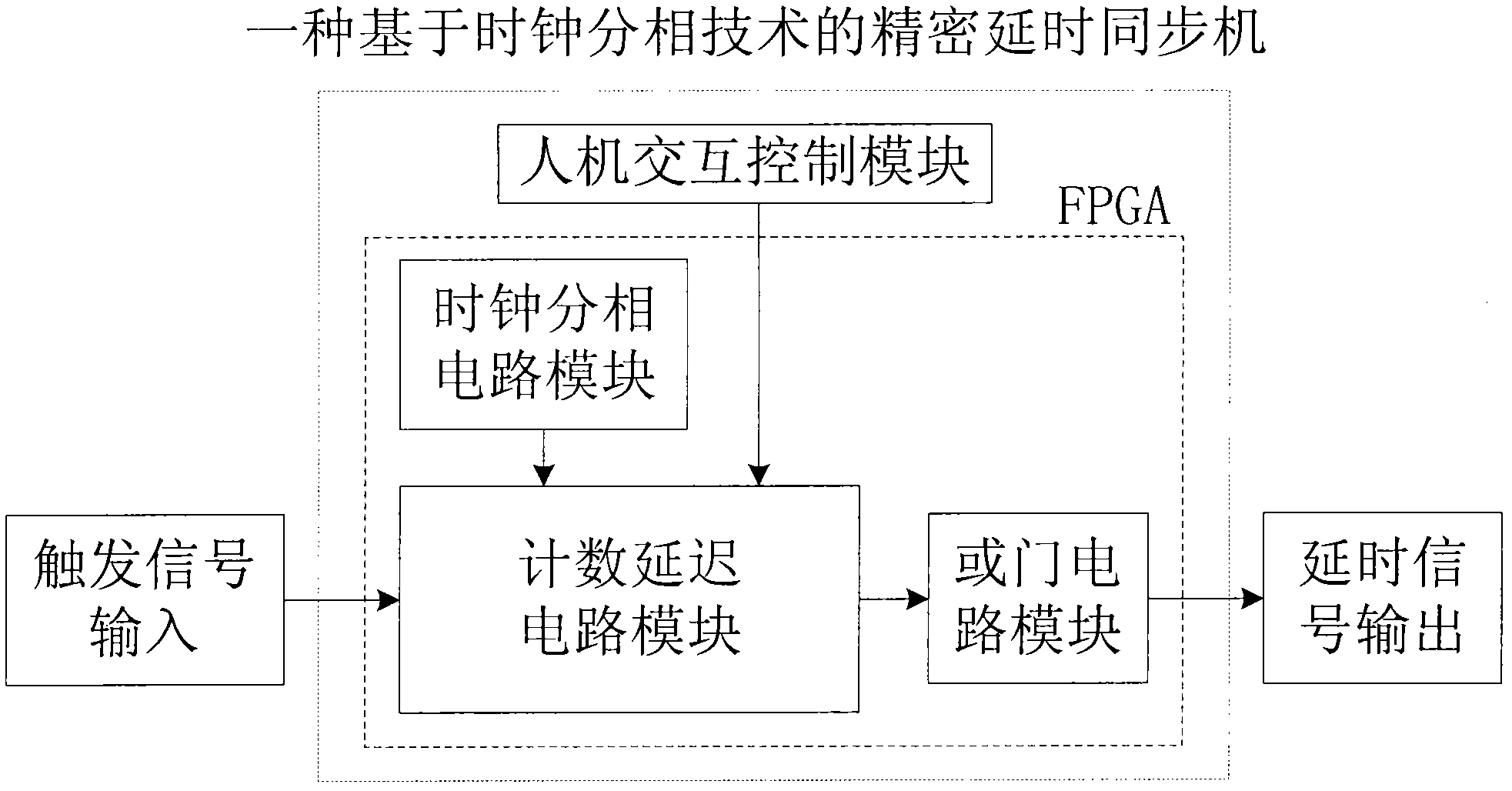

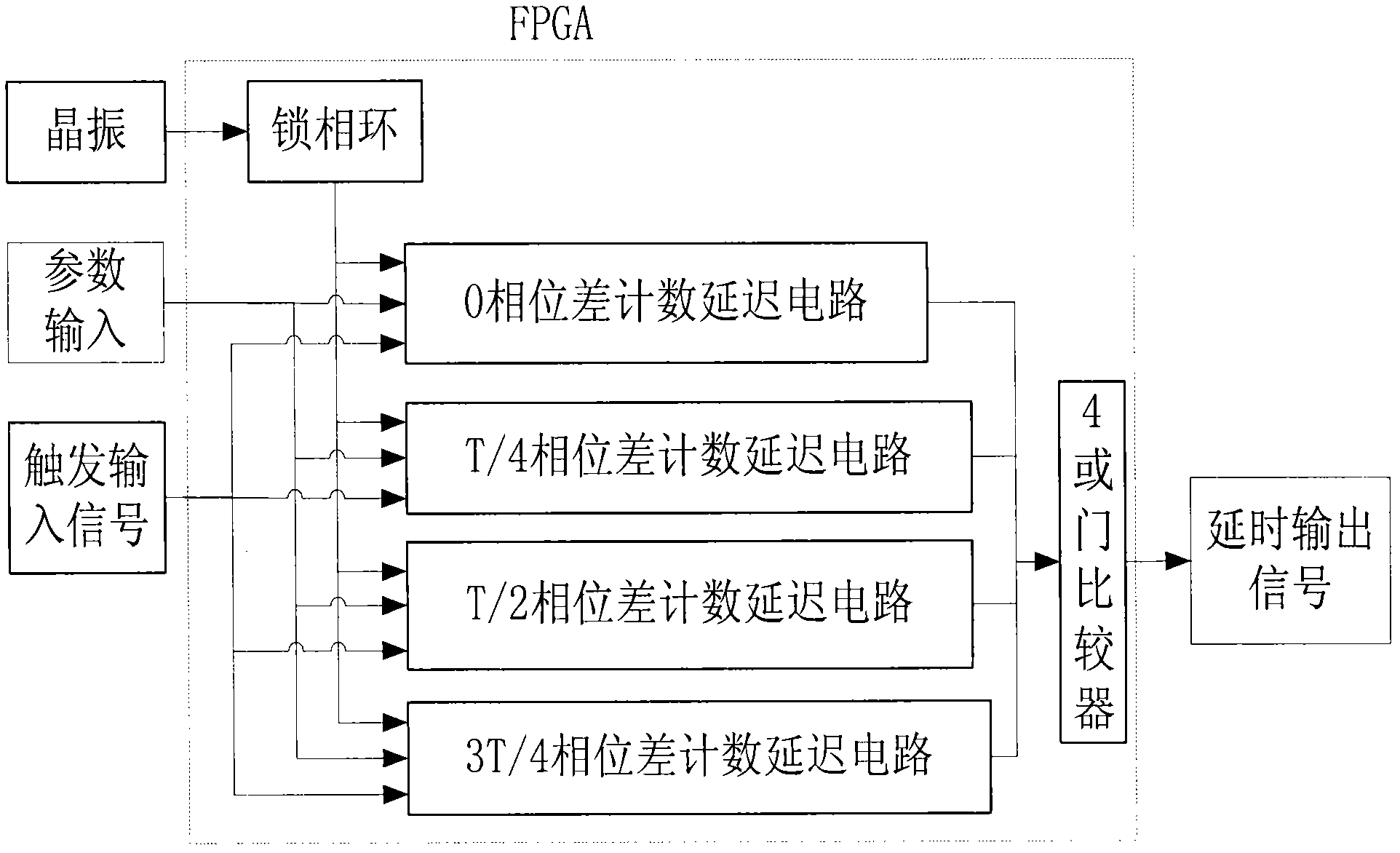

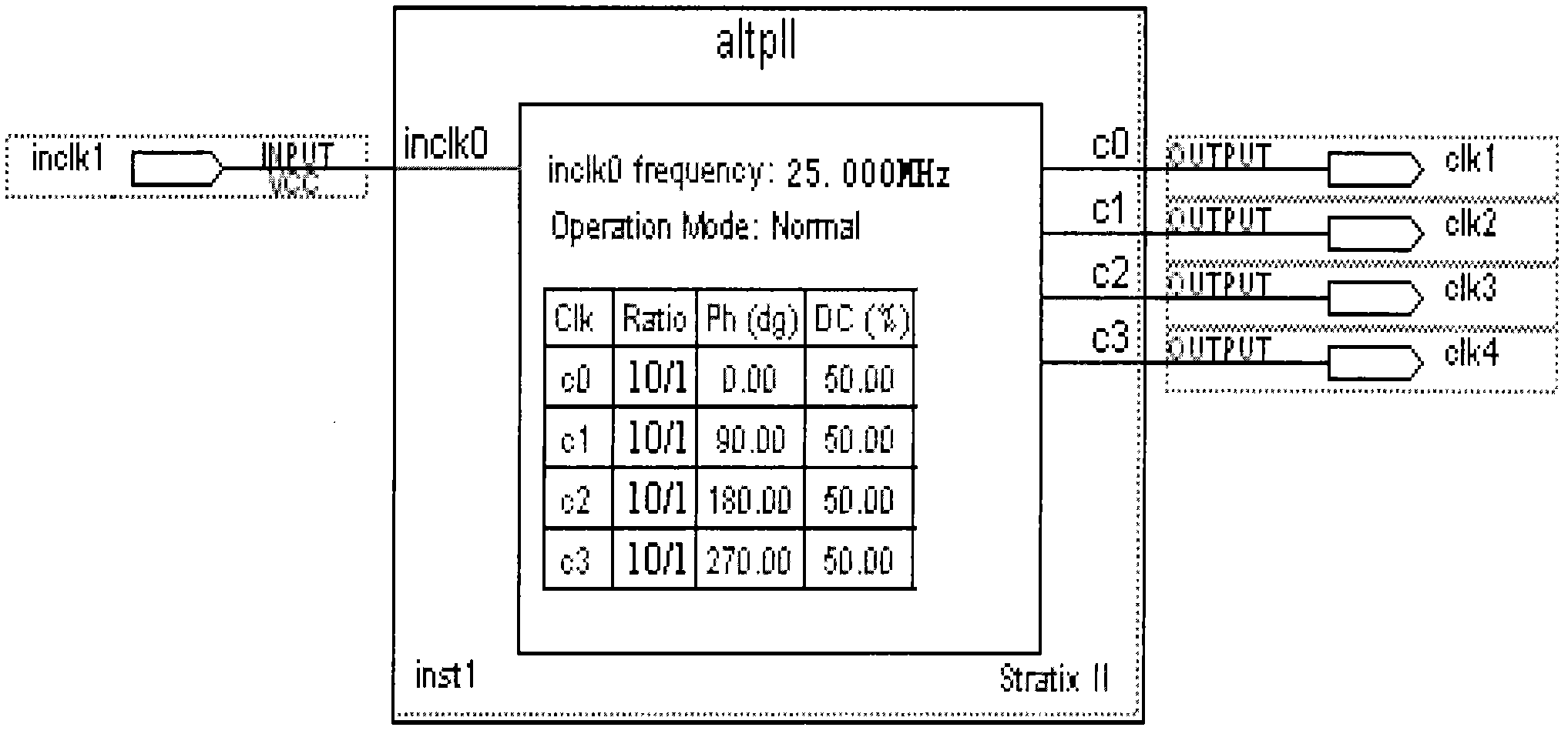

[0022] System principle analysis: the present invention adopts clock phase-splitting technology, utilizes VHDL language and schematic diagram mixed programming design to complete the precision digital time-delay synchronous machine design based on clock phase-splitting technology by FPGA (field programmable gate array). In this design, a low-frequency, high-precision crystal oscillator is used as a clock source, and a high-stability, low-jitter phase-splitting clock is obtained through this low-frequency clock through a phase-locked loop (PLL). Using a multi-stage phase-splitting clock, the cloc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More