Precision digital delay synchronization method based on phase compensation

A digital delay and phase compensation technology, applied in pulse processing, electrical components, pulse technology, etc., can solve the problems of delay precision operating frequency limitation, low integration, large trigger jitter, etc., to improve the delay resolution , The circuit is simple and reliable, and the effect of reducing the trigger error

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

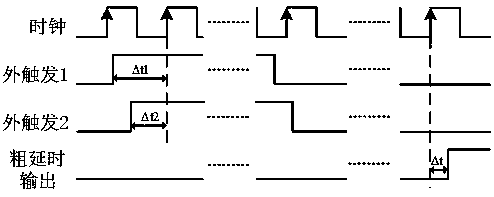

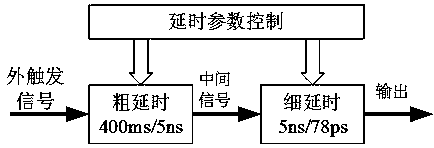

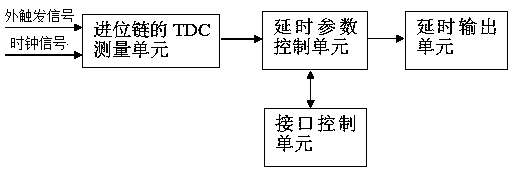

[0028] Such as figure 1 As shown, the circuit mainly includes a TDC based on a carry chain, a delay parameter control unit and a delay output unit. TDC is divided into two parts: time measurement and encoding circuit: time measurement is to introduce the external trigger signal to the special carry chain of FPGA, each carry chain delay unit is realized by the basic structure of FPGA, and each delay unit is followed by a register, which can Ensure that the current delay value is latched and output immediately when the clock edge arrives; and then through the back-end encoding circuit, the time interval between the external trigger signal and the rising edge of the next clock CLK can be obtained. The delay parameter control unit combines the phase relationship between the external trigger and the local clock and the preset delay parameters to calculate, and obtains the corresponding coarse count value and fine delay series. By setting the delay output unit, the delay output aft...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More