Differential structure single-gate memory applicable to ultra high frequency (UHF) radio frequency identification device (RFID) passive label chip

A differential structure and memory technology, applied in the field of microelectronics, can solve the problems of incompatibility with CMOS technology, affect the popularization and application of RFID tags, and high cost, and achieve the effect of reducing technology development cycle, shortening time to market, and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Hereinafter, a single-gate semiconductor memory according to an embodiment of the present invention will be described in detail with reference to the accompanying drawings.

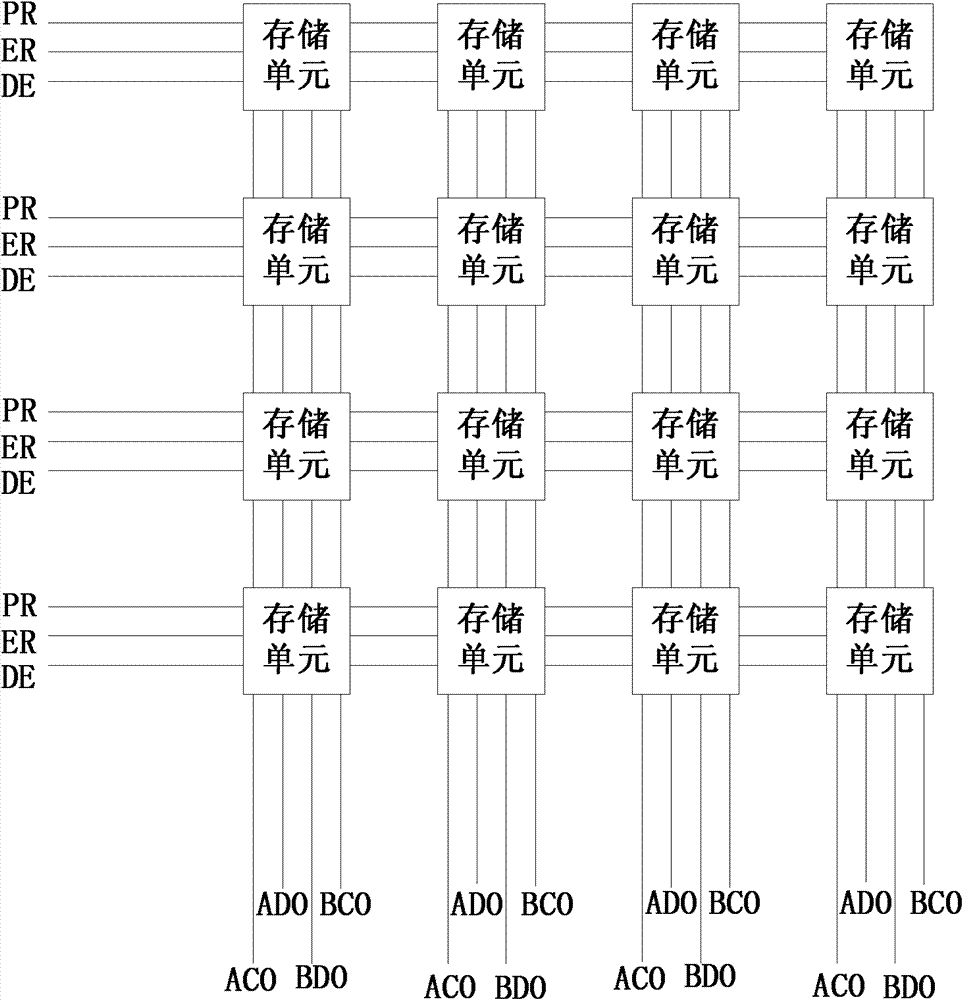

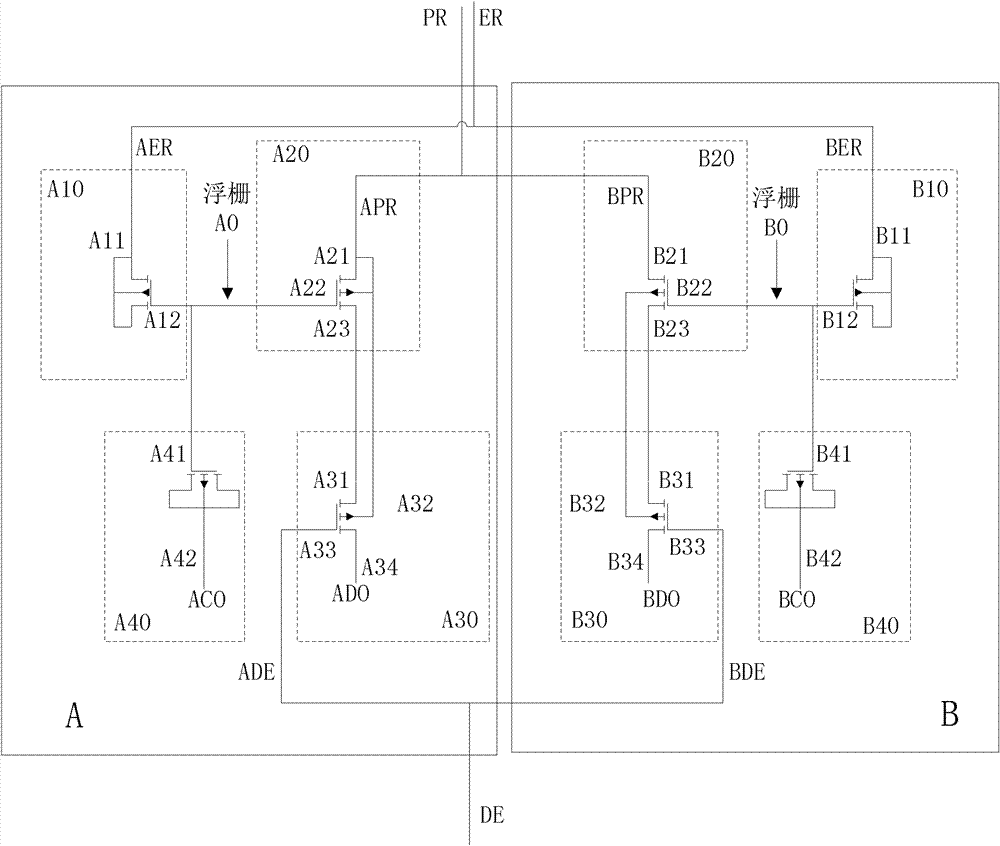

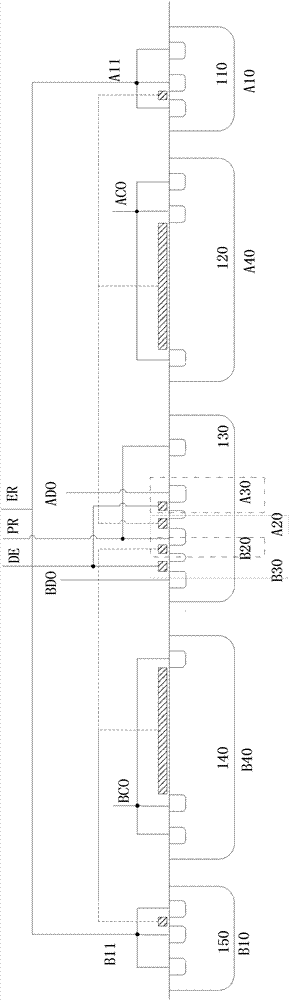

[0022] refer to figure 1 , the present invention is made up of a plurality of identical storage units, and the storage unit of this example is 16, and namely memory capacity is 16, but not limited to 16, and the actual number of storage units is determined according to the required capacity. from figure 1 It can be seen that in each row, the programming terminals PR of all memory cells are connected in parallel, the erasure terminals ER of all memory cells are connected in parallel, and the decoding terminals DE of all memory cells are connected in parallel; in each column , the data output terminals ADO of all storage units are connected in parallel, the data output terminals BDO of all storage units are connected in parallel, the coupling terminals ACO of all storage units are connected in paral...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More