Method for refreshing bulk-silicon floating body cell transistor memory

An operation method and transistor technology, applied in static memory, digital memory information, information storage, etc., can solve problems such as aggravation of negative effects, invalid refresh operation due to incorrect refresh operation, and inability to achieve composite effects, and achieve high reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings.

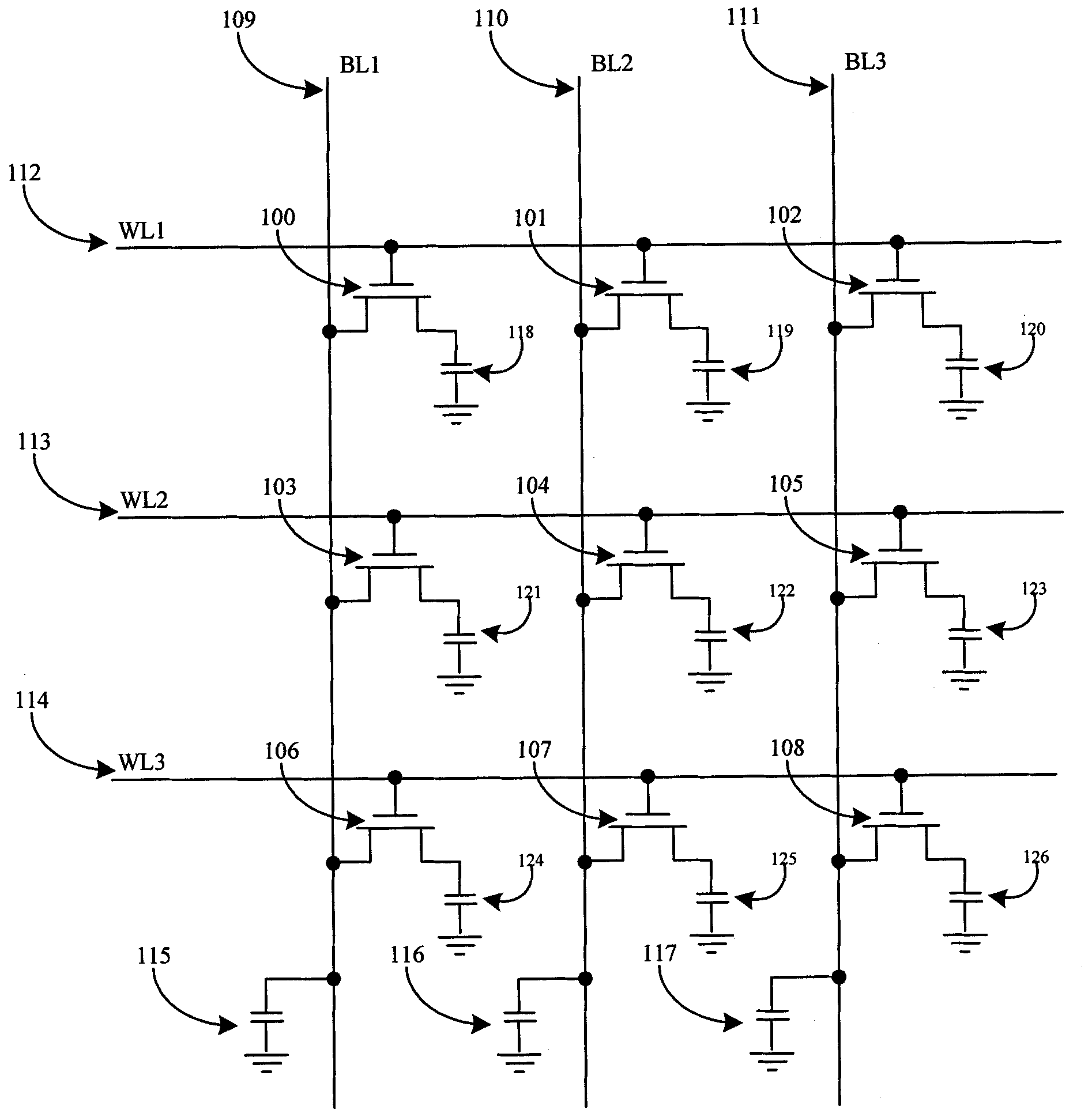

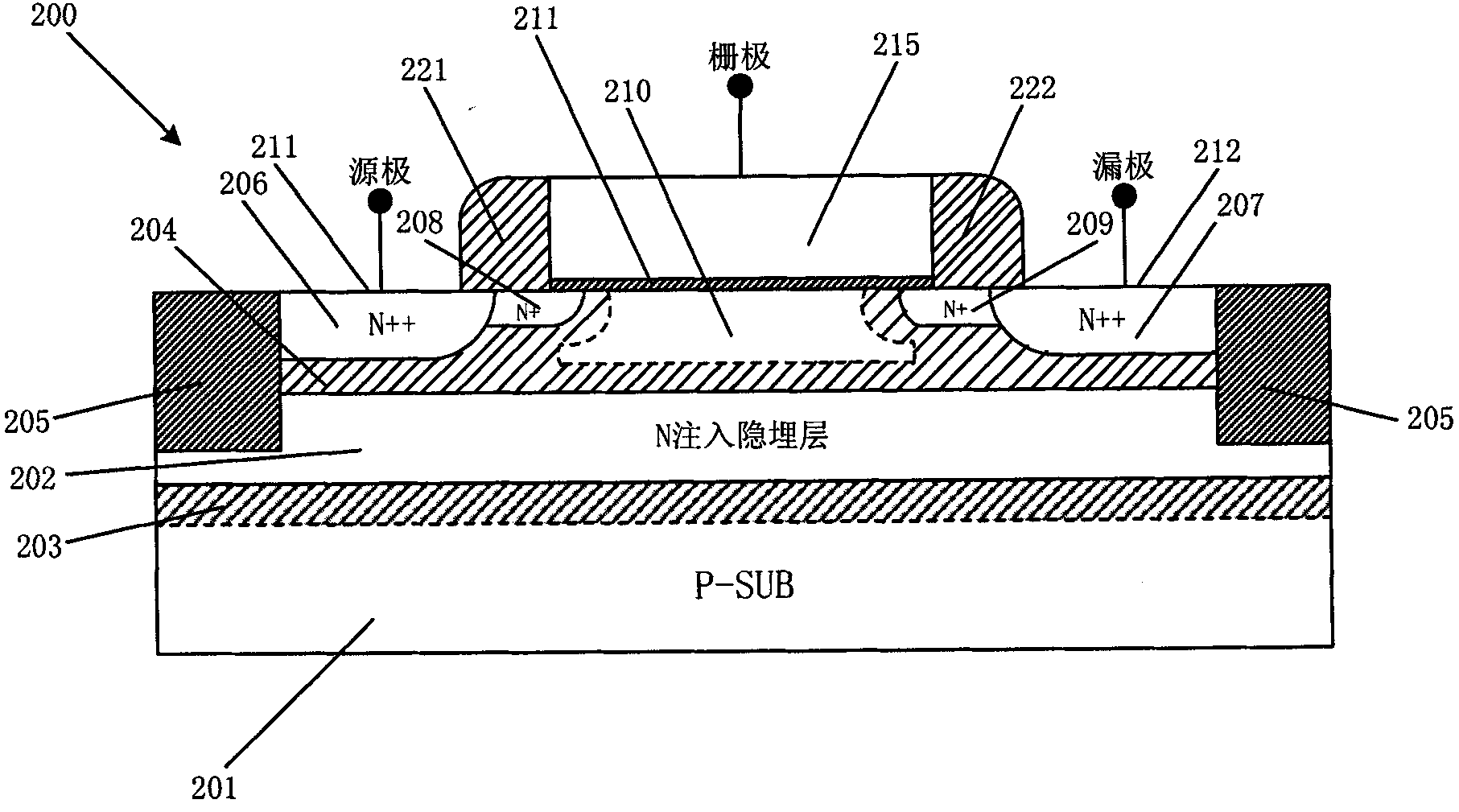

[0047] The refresh operation method provided by the present invention is applicable to FBC memories, and generally applicable to Bulk FBC memories. The refresh operation frequency of the Bulk FBC memory is relatively higher, and the requirement to improve the refresh operation method is more urgent. In the following embodiments, the refresh operation method of the Bulk FBC memory of the NMOS type is taken as an example.

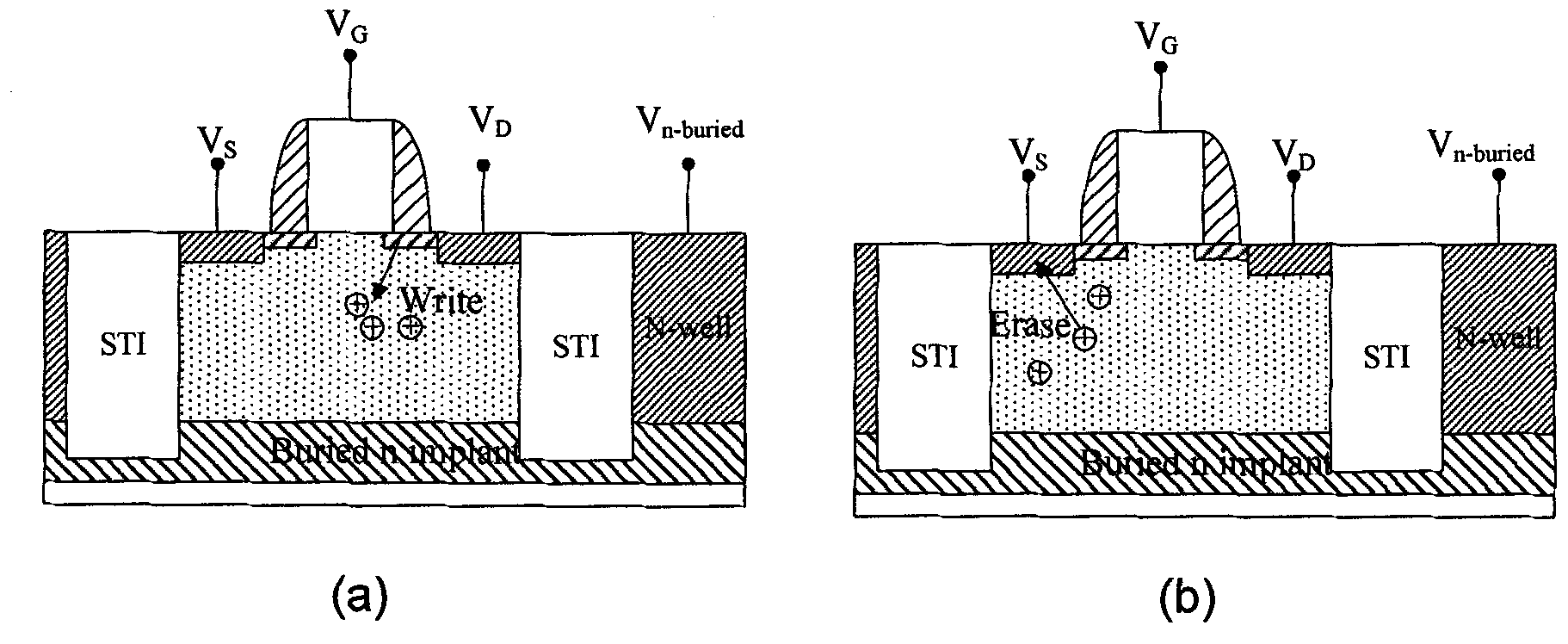

[0048] In Bulk FBC memory, the data state stored in the floating body area will weaken with time. Due to leakage current or radiation interference, the "strong 1" state with a large number of holes will gradually decrease due to the decrease in the amount of holes stored. It becomes a "weak 1" state, and the "strong 0" state where there are no hole...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More