Hardware coprocessing device for high-speed mass data acquisition and storage system

A mass data and storage system technology, applied in the direction of digital variable display, etc., can solve the problems that cannot be well applied to high-speed mass data acquisition systems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

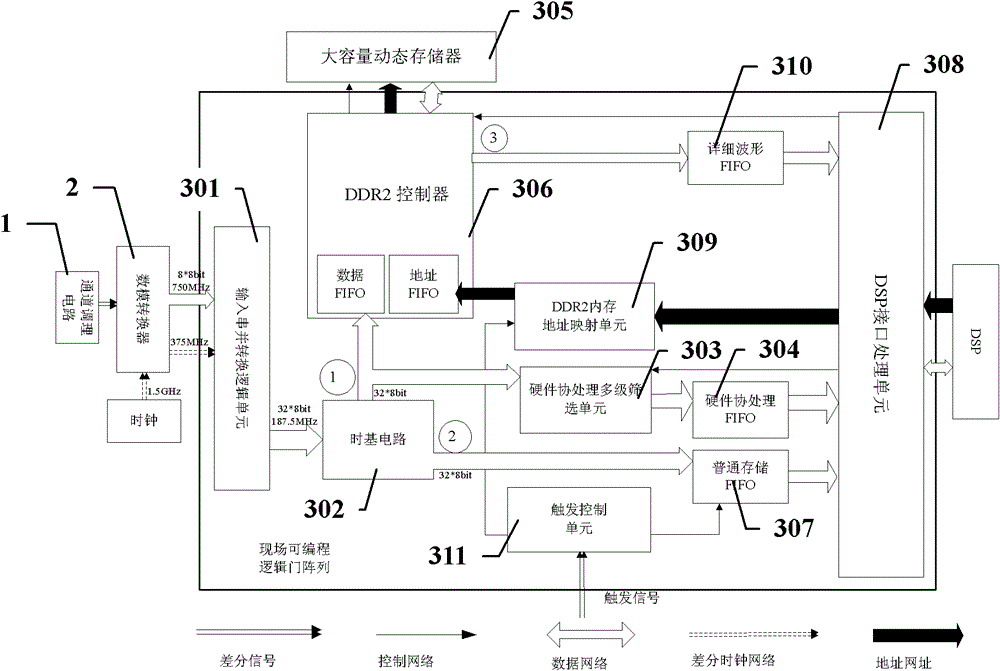

[0042] Such as figure 1 As shown, after the analog signal is conditioned by the channel conditioning circuit 1, the output differential signal is simultaneously sent to the analog-to-digital converter 2 for alternate sampling with a 1.5GHz clock with a phase difference of 90 degrees, and four 1.5GHz data streams are obtained and processed. Serial-to-parallel conversion, output 8 750MHz data streams and 375MHz AD differential clock input FPGA (field programmable logic gate array) for phase-splitting storage.

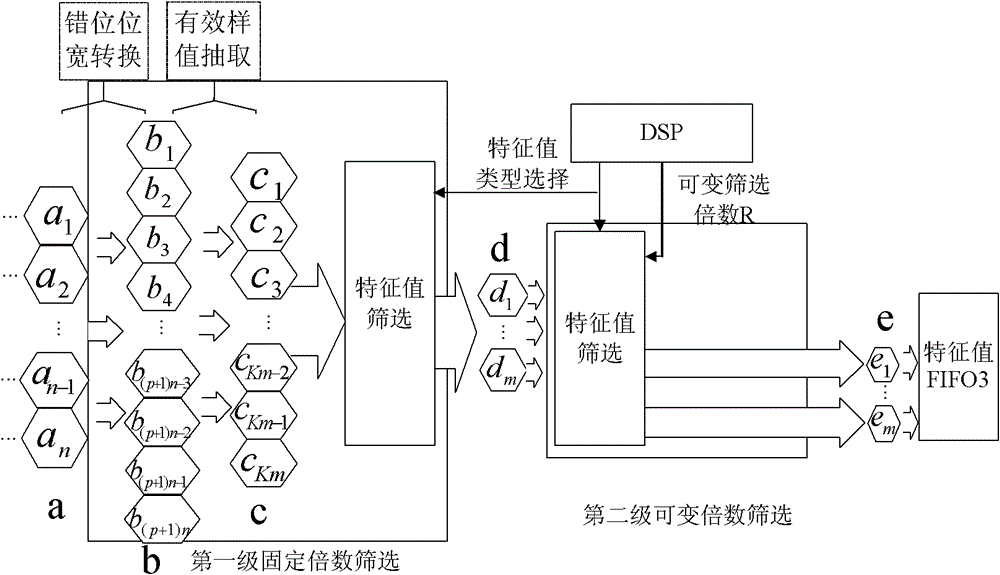

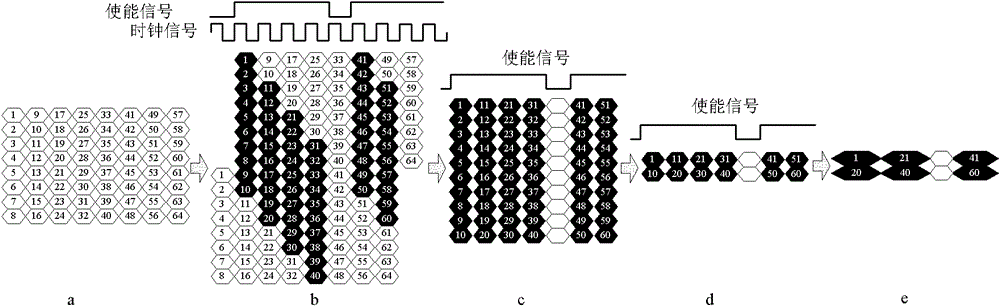

[0043] In this embodiment, the hardware co-processing devices of the high-speed mass data acquisition system are all designed in FPGA except for the large-capacity dynamic memory. Such as figure 1 As shown, the hardware co-processing device of the high-speed mass data acquisition and storage system of the present invention includes an input serial-to-parallel conversion logic unit 301, a time base circuit 302, a hardware co-processing multi-level screening unit 303, a ha...

example

[0108] If the hardware co-processing technology is not used, the system needs T1≈10759.7s to observe the 512Mpts waveform. However, after using hardware co-processing and hardware post-processing technology, the efficiency is significantly improved. Under the condition of storage depth of 512Mpts: set the waveform address quick lock and mapping technology screening ratio to N; there are 10 user-concerned sample data on the screen; the sampling rate is R D ; System efficiency ratio comparison table, as shown in Table 1:

[0109] Table 1 Storage efficiency comparison table

[0110]

[0111]

[0112] Table 1

[0113] The results show that the efficiency and waveform capture rate of the system can be greatly improved by adopting technologies such as multi-level screening and address quick lock under hardware co-processing, hardware post-processing and FIFO real-time control.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More