Low-heat-resistance packaging structure of power MOS (Metal Oxide Semiconductor) device

A technology of MOS devices and packaging structures, which is applied in the direction of electric solid-state devices, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problem of reducing the thermal resistance and parasitic inductance of MOS devices, not being compatible with existing technologies, and pin packaging Form differences and other issues, to achieve the effect of reducing the body inductance, reducing thermal resistance, and reducing thermal resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

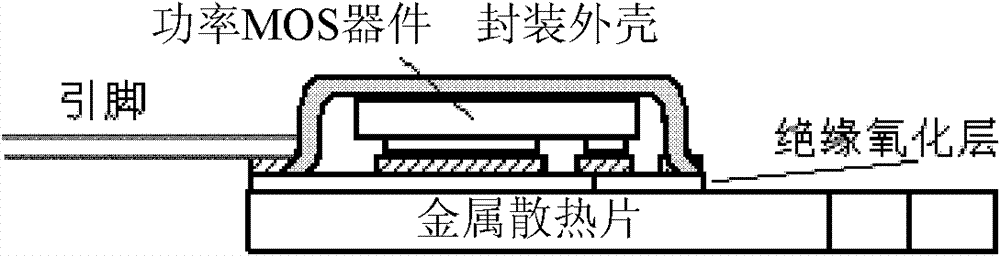

[0019] A low thermal resistance packaging structure for power MOS devices, such as image 3 Shown, including the power MOS device, metal heat sink, package case, and gate, source, and drain external pins. The surface of the metal heat sink has a thin layer of insulating oxide; the surface of the thin layer of insulating oxide has gate, source and drain metal pads corresponding to the gate, source and drain of the power MOS device; the power MOS device Flip-chip on the thin layer insulating oxide surface of the metal heat sink; the gate, source and drain of the power MOS device are respectively welded to the gate, source and drain metal pads on the thin layer insulating oxide surface; thin The gate, source and drain metal pads on the surface of the insulating oxide layer are respectively connected to the external pins of the gate, source and drain; the package shell is installed outside the power MOS device to realize the isolation of the power MOS device from the external envi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More