Thermal-expandability three-dimensional parallel cooling integration method, namely, on-chip system key technology for massively parallel computation

An integration method and heat sink technology, applied in computing, special data processing applications, instruments, etc., can solve problems such as limitations, inability to maximize device layer performance, and inability to achieve thermal expansion with three-dimensional vertical integration technology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

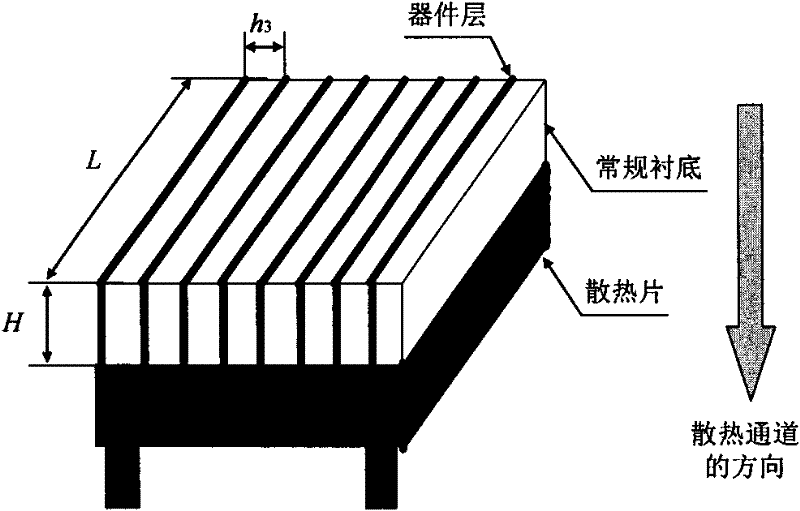

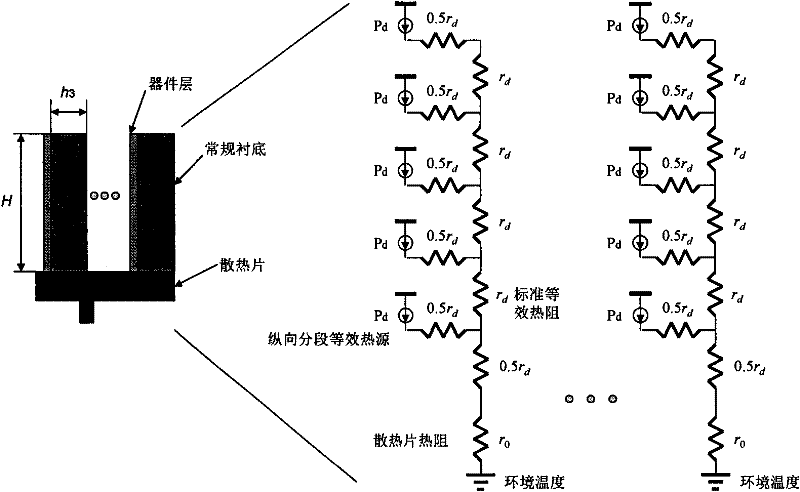

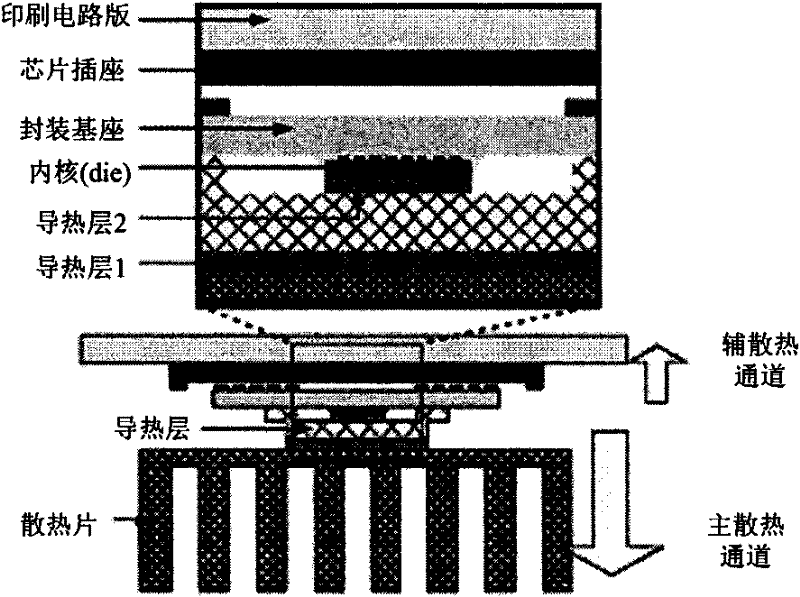

[0037] The invention proposes a thermally expandable 3D parallel heat dissipation integration method, and theoretically illustrates the thermal expandability of the invention. The specific steps are as follows: conduct full-chip 3D static thermal analysis of the 2D chip, and simplify the static thermal analysis model of the 2D chip. Based on the simplified static thermal analysis model of 2D chips, the present invention first models the heat dissipation problem of 3D vertically integrated chips, and derives the accurate calculation of the highest substrate temperature T of 3D chips. chip An analytical expression for T that indicates that T chip It is a quadratic polynomial function about the number M of vertically stacked layers of 3D chips, which theoretically proves that the existing 3D vertical integration technology has inherent limitations of thermal inextensibility. An analytical model for calculating the maximum substrate temperature of a 3D parallel cooling integrated...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More