System and method for realizing parallel decompression of hardware

A hardware implementation and decompression technology, applied in electrical components, code conversion, etc., can solve problems such as occupying large CPU resources, low efficiency, and unsuitable for hardware implementation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be described and illustrated more fully below with exemplary embodiments of the present invention with reference to the accompanying drawings.

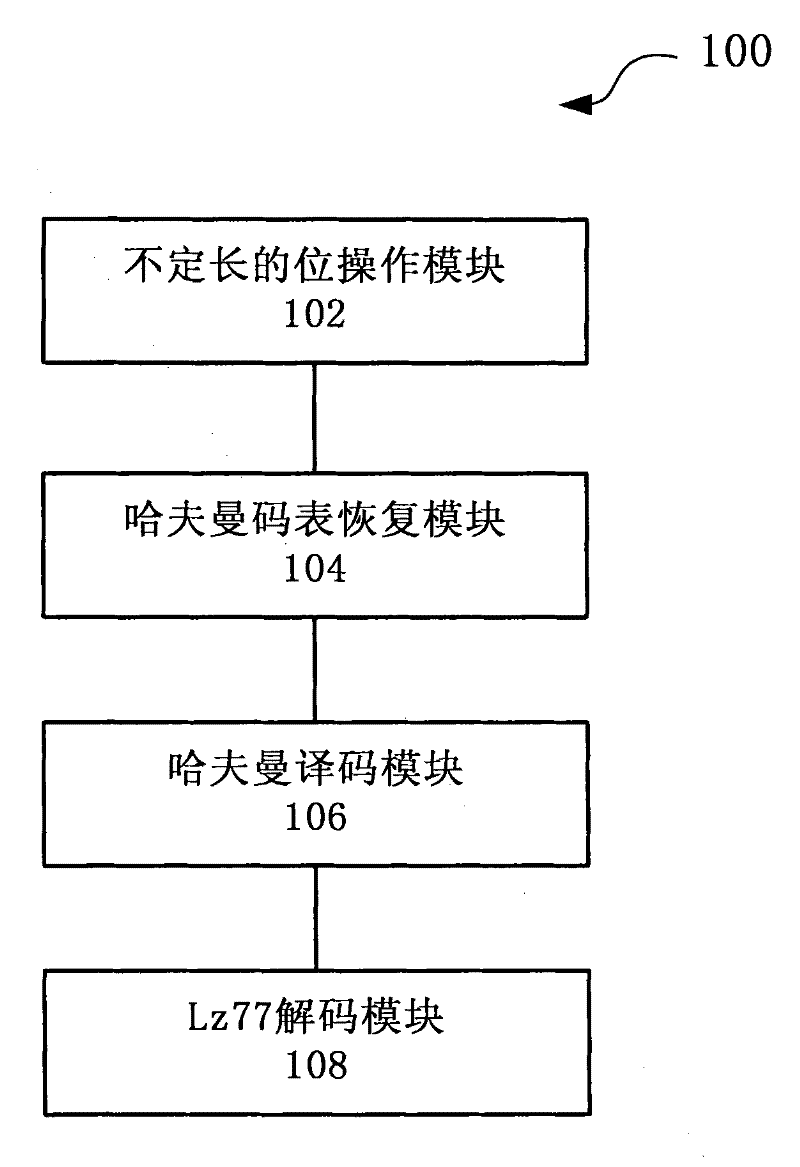

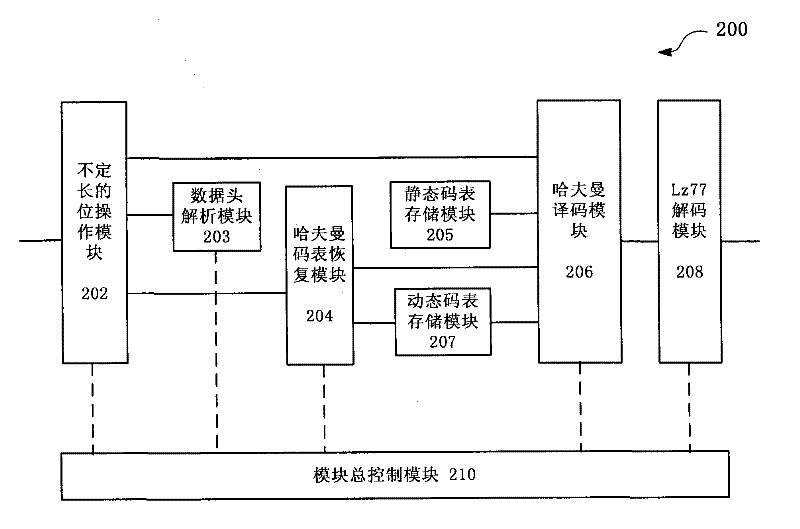

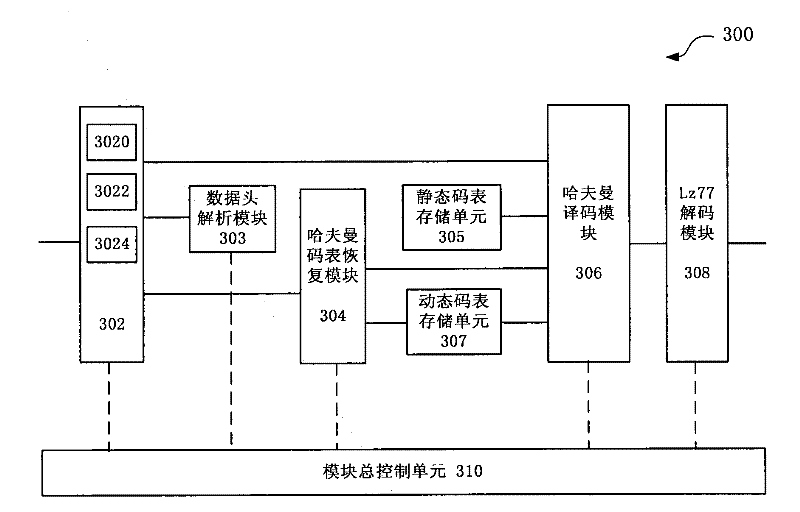

[0042] figure 1 A schematic structural diagram of a hardware-implemented system for parallel decompression provided by an embodiment of the present invention is shown.

[0043] Such as figure 1 As shown, a hardware implementation system 100 for parallel decompression includes: a variable-length bit operation module 102 , a Huffman code table recovery module 104 , a Huffman decoding module 106 and an Lz77 decoding module 108 .

[0044] Among them, the variable-length bit operation module (Bitwise_management) 102 is used to perform variable-length bit operations on the data to be decompressed to obtain variable-length data. For example, the variable-length bit operation module 102 is used to read new data from the first-in-first-out module (In_FIFO_if), output the data of the data bit width used in th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More