A Modeling and Simulation Method of In-machine Testing Based on State Diagram

A simulation method and state diagram technology, applied in special data processing applications, instruments, electrical digital data processing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

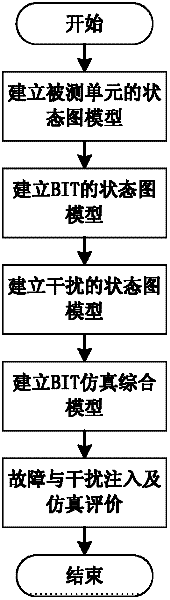

Method used

Image

Examples

Embodiment

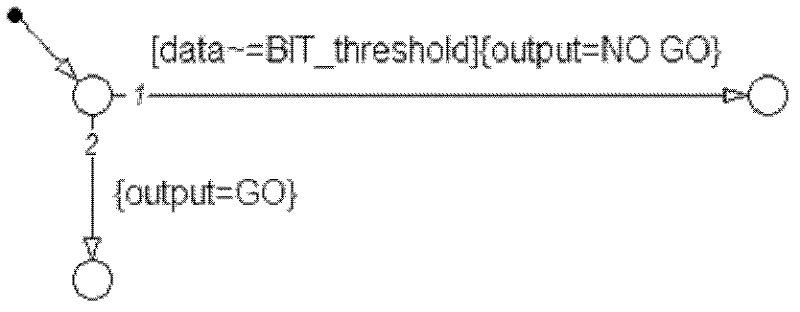

[0184] The method of the present invention will be described below by taking the CPU board and the BIT of the central alarm computer of a certain equipment integrated avionics system as an example.

[0185] The CPU board BIT state diagram simulation comprehensive model is composed of 4 modules: UUT, interference, test BIT, integrated management BIT, several fault modes selected in the case, and their normal values, fault values and fault codes, as shown in Table 11 .

[0186] Table 11 Case Failure Modes

[0187]

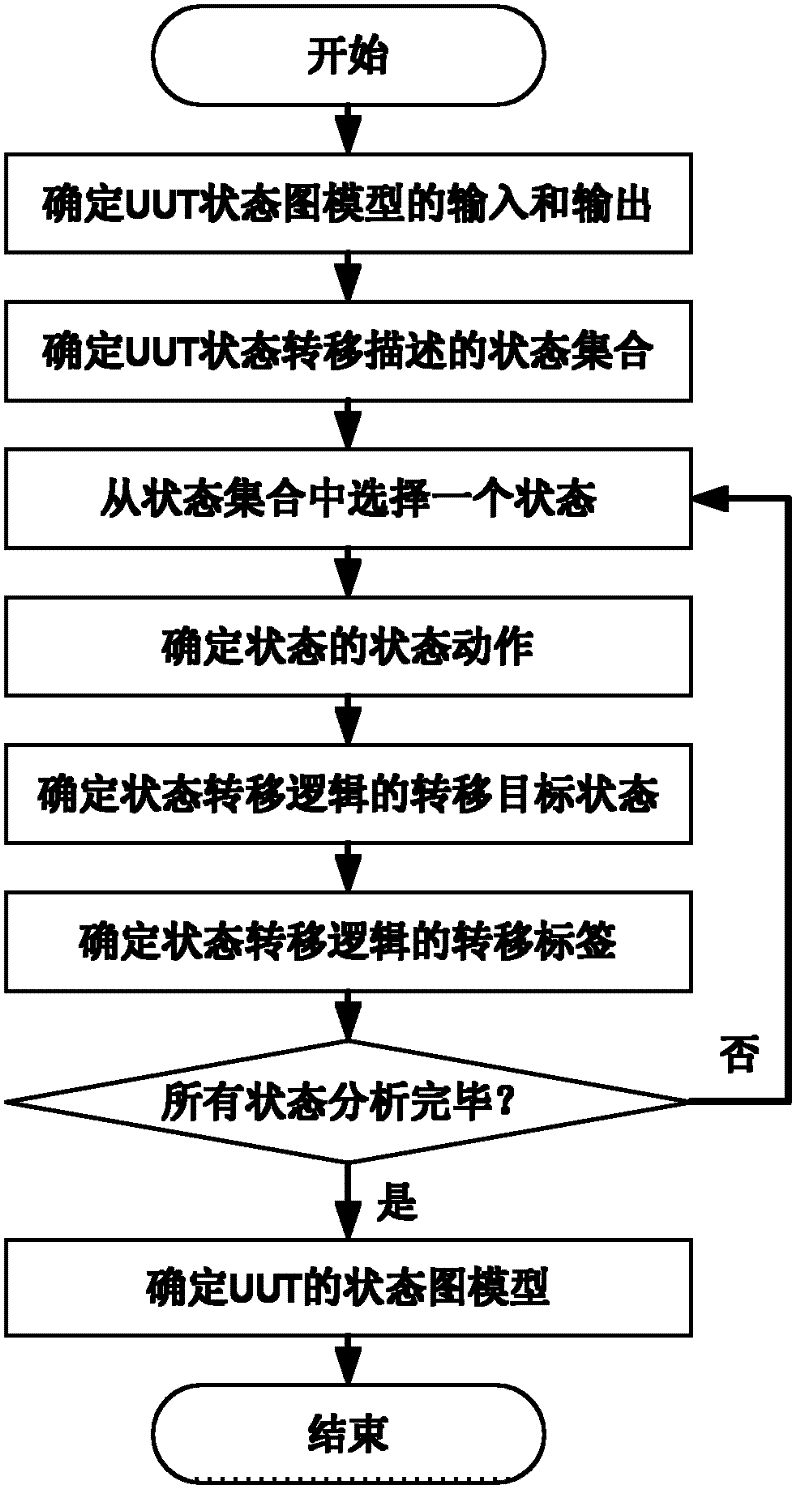

[0188] Step 1: Establish a state diagram model of the CPU board

[0189] (1) Input of CPU board state diagram model

[0190] The input of the CPU board state diagram model is shown in Table 12.

[0191] Table 12 Input of CPU board state diagram model

[0192]

[0193] (2) Output of CPU board state diagram model

[0194] The output of the CPU board state diagram model is shown in Table 13.

[0195] Table 13 Output of CPU board state diagram model

[019...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More