On-chip Auxiliary Test System and Auxiliary Test Method for δς Analog-to-Digital Converter

An analog-to-digital converter and auxiliary test technology, which is applied in the direction of electronic circuit testing, etc., can solve problems affecting the performance of the ΔΣ analog-to-digital converter and interfere with the working state, and achieve the effect of reducing the difficulty of testing and reducing the interference of testing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

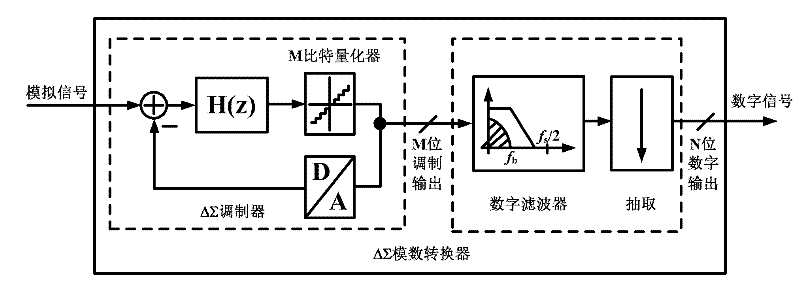

[0027] The present invention proposes an on-chip auxiliary test system of a ΔΣ analog-to-digital converter and a test method thereof in conjunction with accompanying drawings and embodiments as follows:

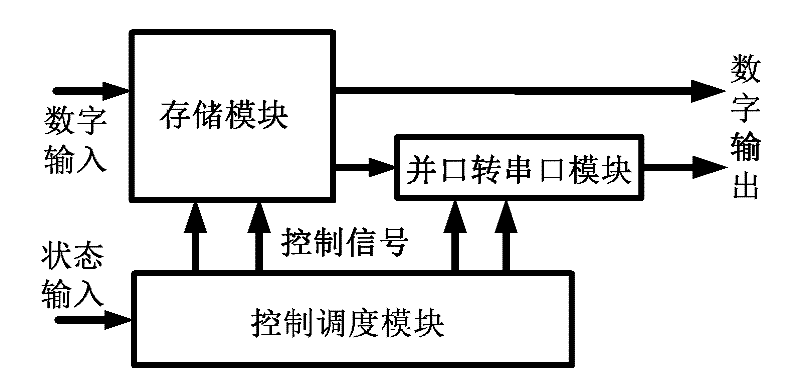

[0028] The on-chip auxiliary test system of the ΔΣ analog-to-digital converter of the present invention, such as image 3 As shown; it is characterized in that it includes a memory module integrated on the ΔΣ analog-to-digital converter chip, a parallel port to serial port module, and a control scheduling module; the memory module is used to store the ΔΣ modulator or the ΔΣ analog-to-digital conversion The output digital code of the device (store the output digital inside the chip first, and then take it out when testing); the parallel port to serial port module is used to convert N-bit parallel output digital to N serial output digital (can reduce the output PAD ); the control scheduling module is used to generate control signals for scheduling each module to realize the aux...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More