Performance acceleration method of heterogeneous multi-core computing platform on chip

A heterogeneous multi-core, computing platform technology, applied in general-purpose stored program computers, multi-programming devices, architectures with multiple processing units, etc. Efficient division, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

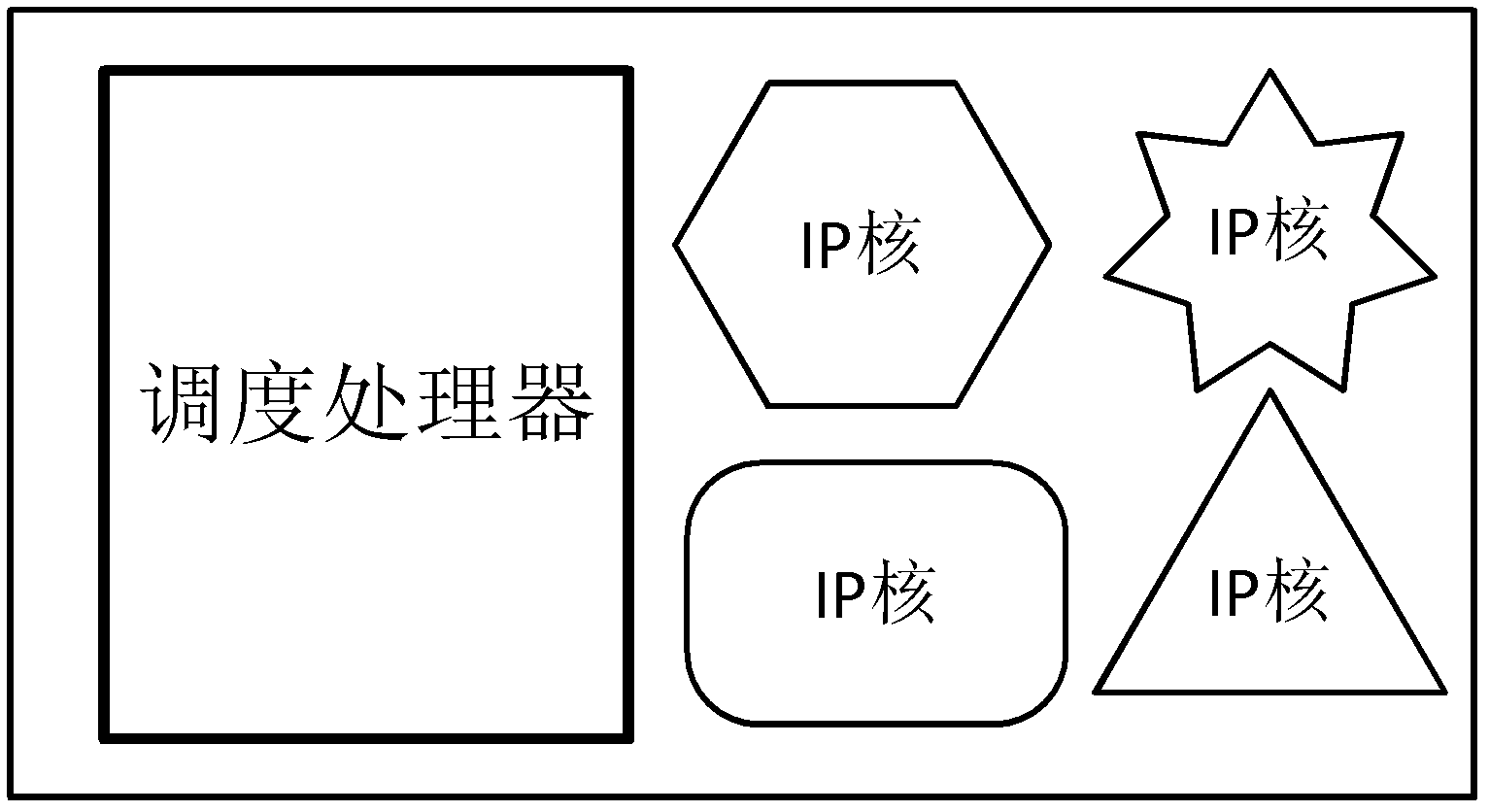

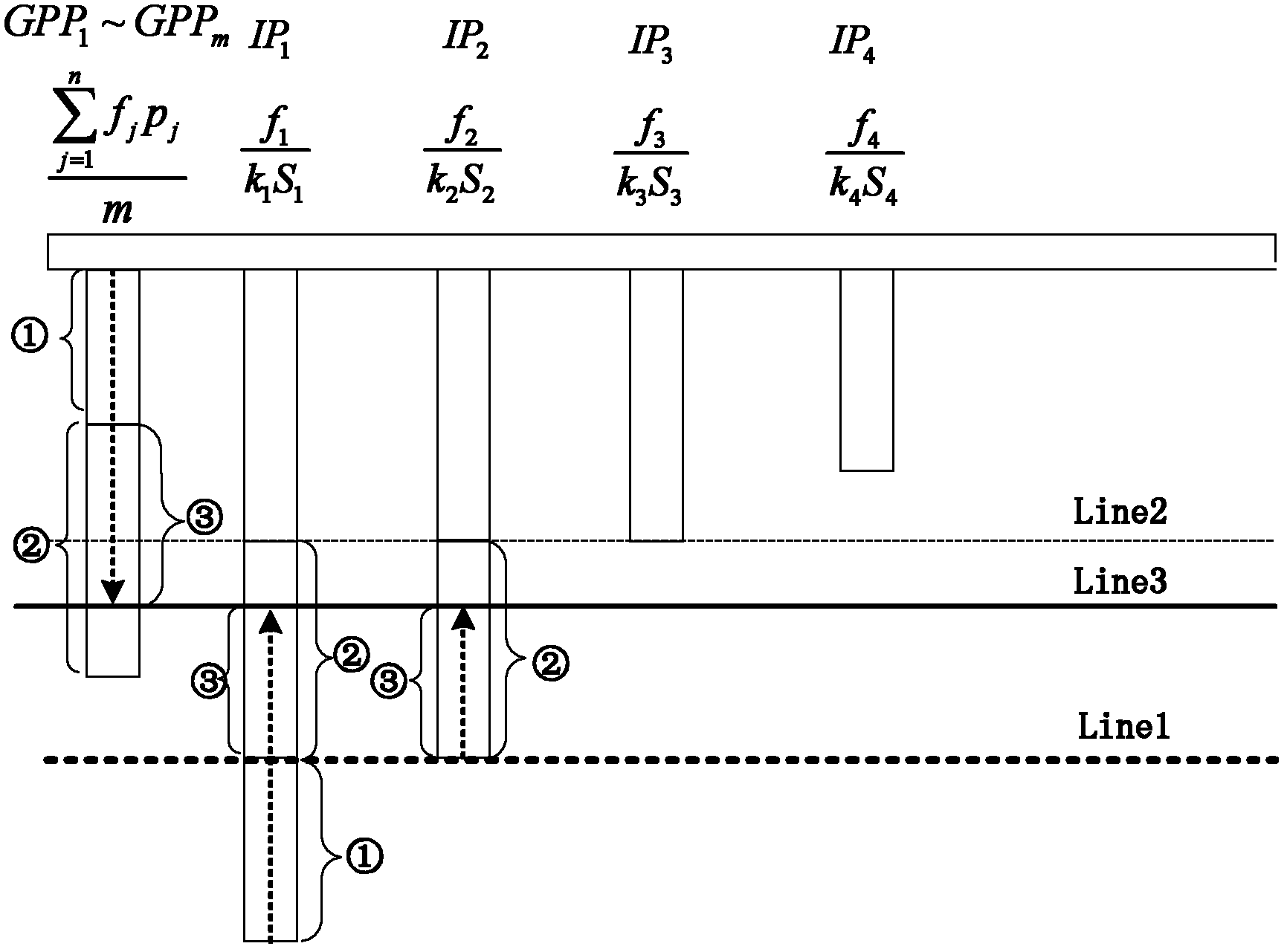

[0030] The main difference between a heterogeneous multi-core system and a homogeneous multi-core system is that the operations that can be accelerated cannot be allocated to all acceleration components, but can only be allocated to specific components to run, so the speedup ratio of the system is limited Acceleration component with the longest running time. This embodiment first considers only the hardware acceleration component IP core, and the hardware acceleration component IP core of each function has only one simplified architecture, such as figure 1shown. The task scheduling system of the on-chip multi-core computing platform includes a task division module and multiple hardware IP cores. The task division module divides the task requests into different hardware IP cores for execution through the attributes of the tasks and the current operating status of the system.

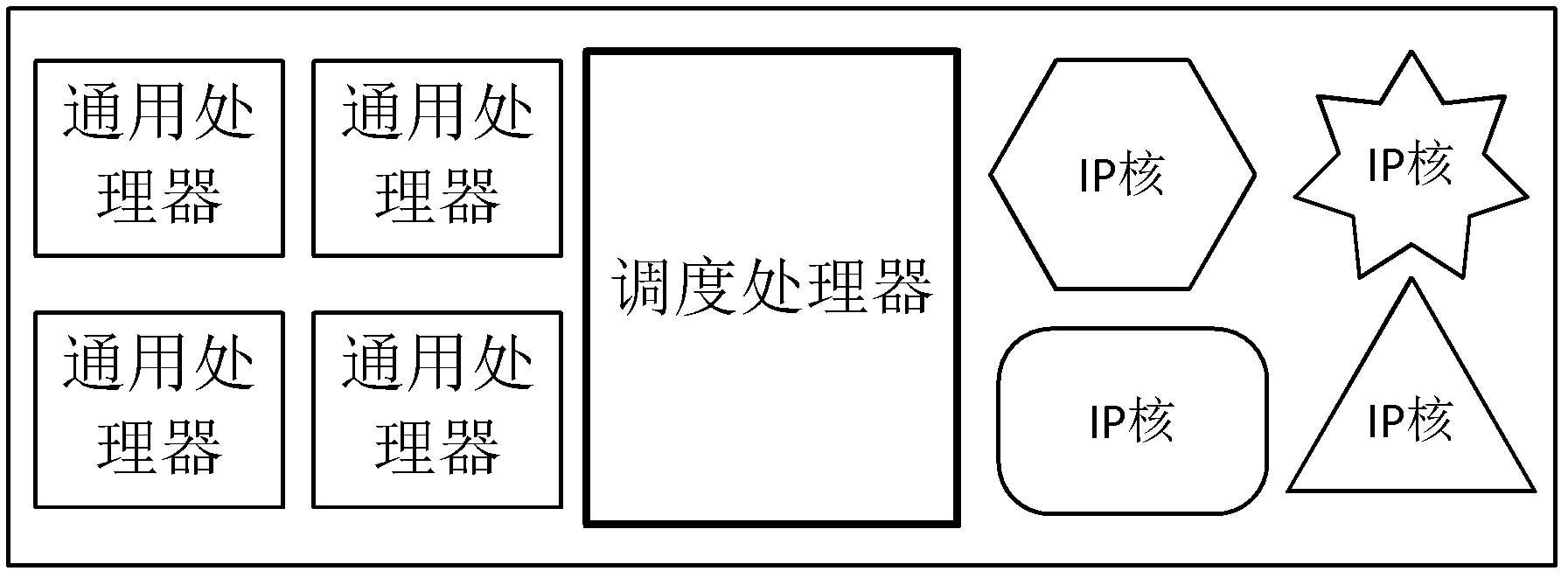

[0031] First, classify the general-purpose processors and IP cores of the same type in the platform,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More