Low output ripple wave parallel power-factor correction (PFC) transform control method and device

A power factor correction and conversion control technology, which is applied in the direction of output power conversion device, sustainable manufacturing/processing, high-efficiency power electronic conversion, etc., can solve the problems of large DC output voltage ripple, low efficiency, and high cost of converter design , to increase the cut-off frequency, reduce the DC output voltage/current ripple, and improve the efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment example

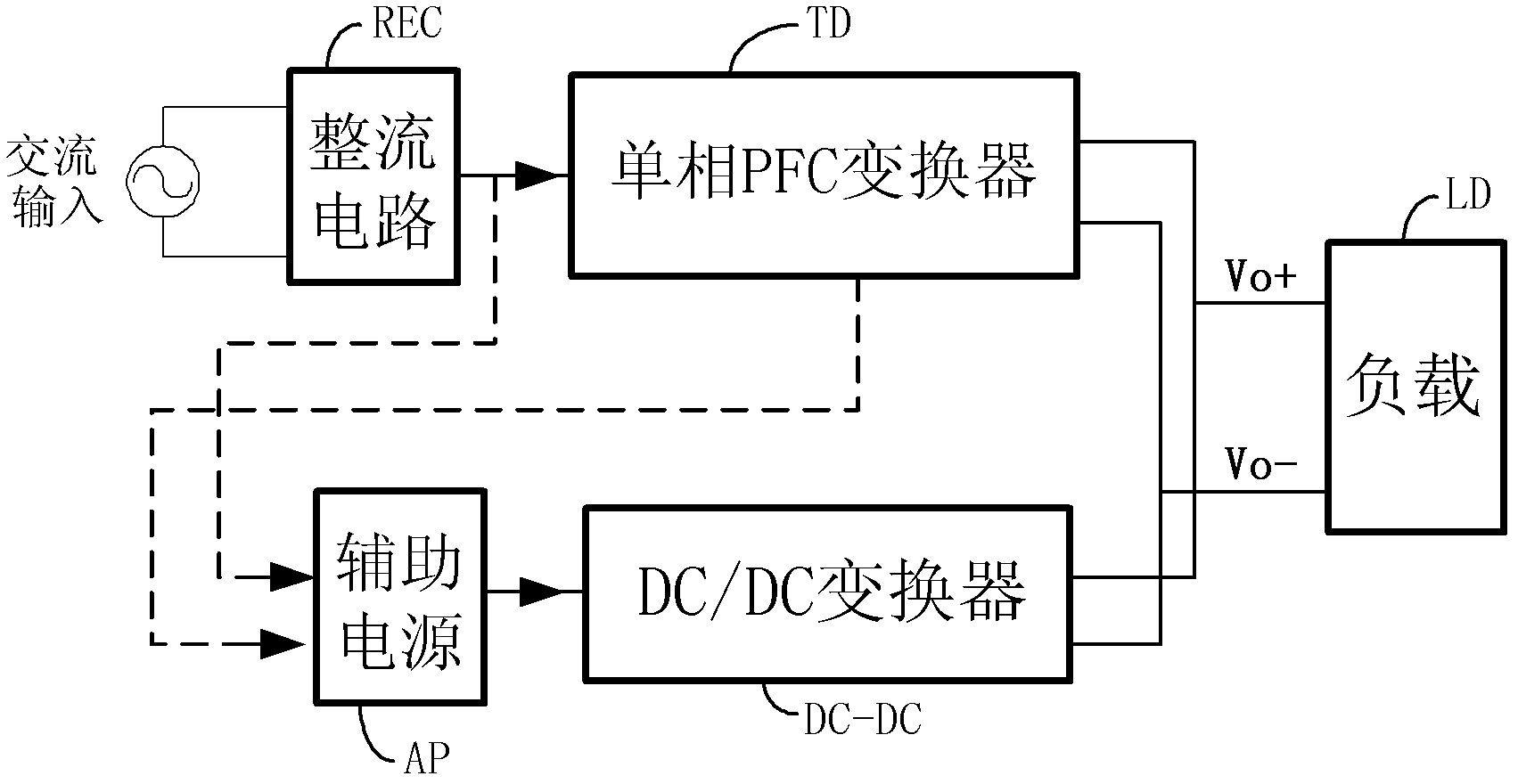

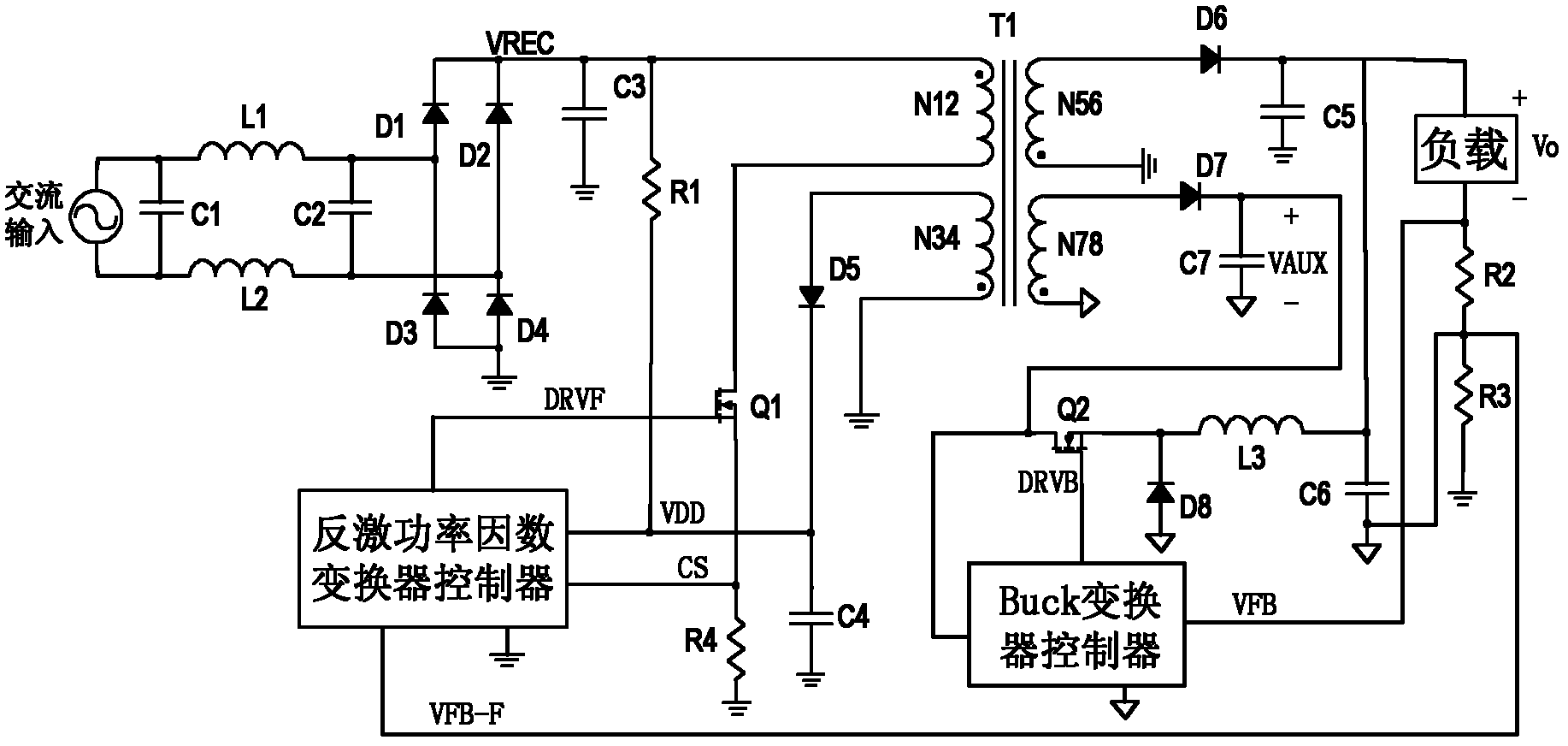

[0021] figure 2 It is shown that a specific embodiment of the present invention is a topology and control method of a constant current source switching power supply, and its specific method is:

[0022] The AC input power is connected to the rectifier bridge composed of D1, D2, D3, and D4 through the LC filter network of C1, C2, L1, and L2. The rectifier bridge outputs the VREC signal as the input of the flyback converter, and the transformer of the flyback converter T1 has 4 windings N12, N34, N56 and N78, N12 is the primary winding; N34 is the auxiliary winding that provides power to the flyback power factor controller, through D5, C4 generates VDD voltage to provide power to the flyback power factor controller ; N56 is the main output winding of the flyback converter, N56 winding passes through D6, C5 generates Vo+ to provide part of the energy for the load; N78 is another set of output windings of the flyback converter, N78 generates auxiliary power VAUX through D7 and C7...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More