Heterojunction with intrinsic thin layer (HIT) solar cell structure with heterogeneous floating junction back passivation, and preparation process thereof

A solar cell and preparation process technology, applied in the field of solar cells, can solve the problems of increased photo-generated carrier recombination, attenuation of amorphous silicon cell efficiency, reduction of quantum efficiency of amorphous silicon thin film cells, etc., and achieves low surface recombination rate, Good open circuit voltage, improving open voltage and overall efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

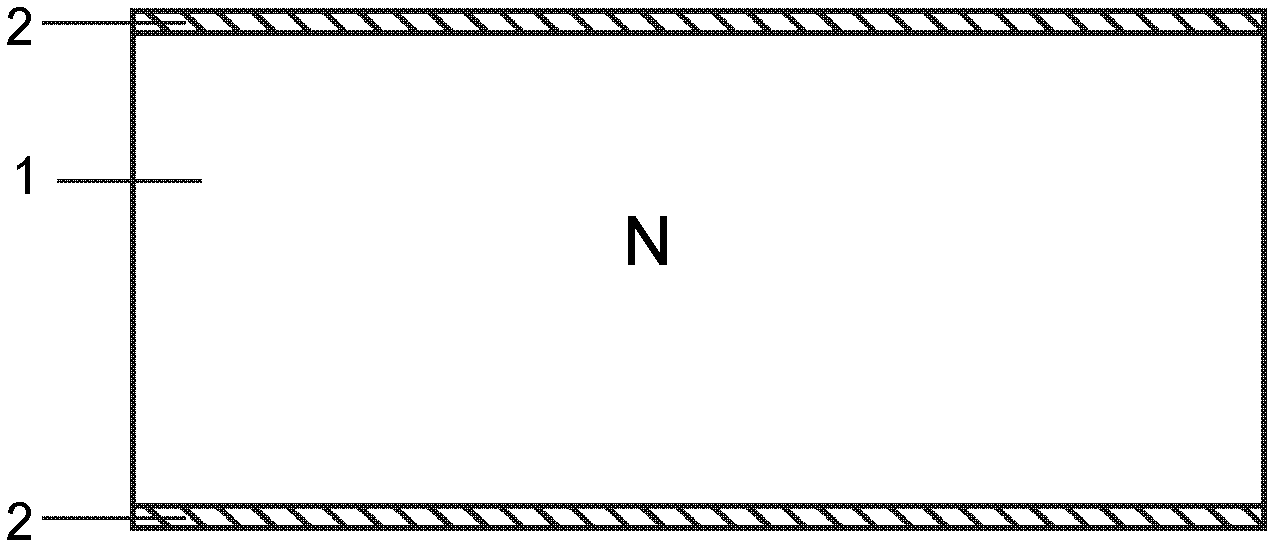

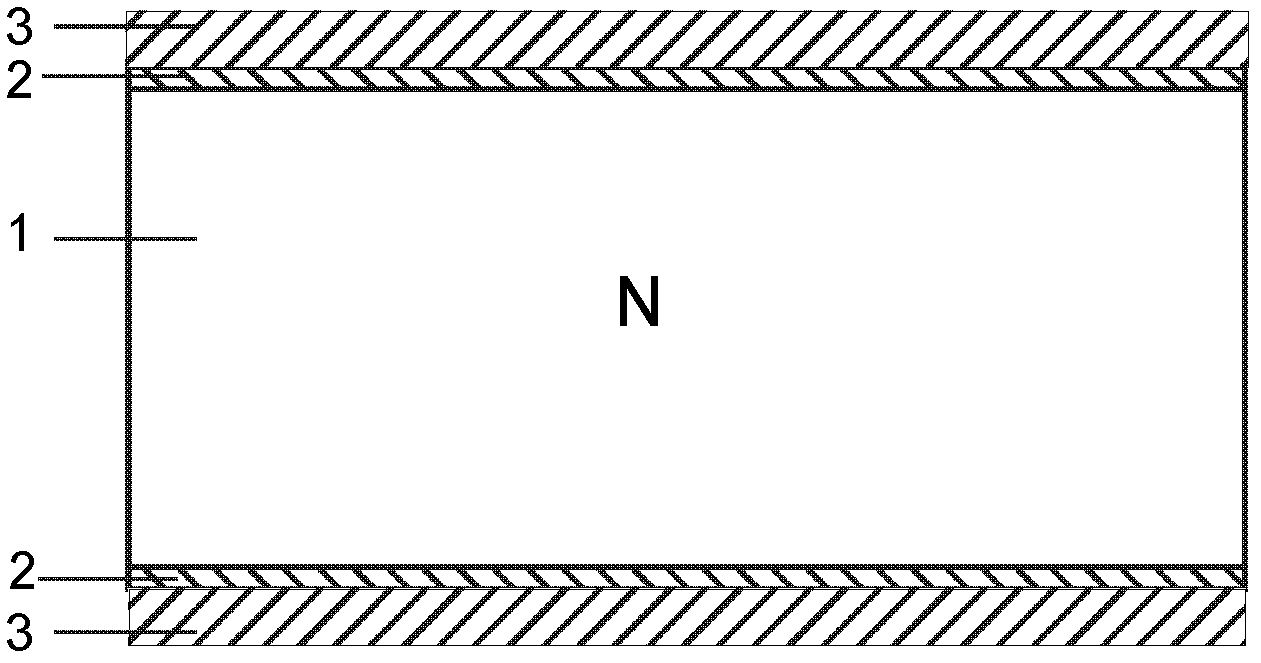

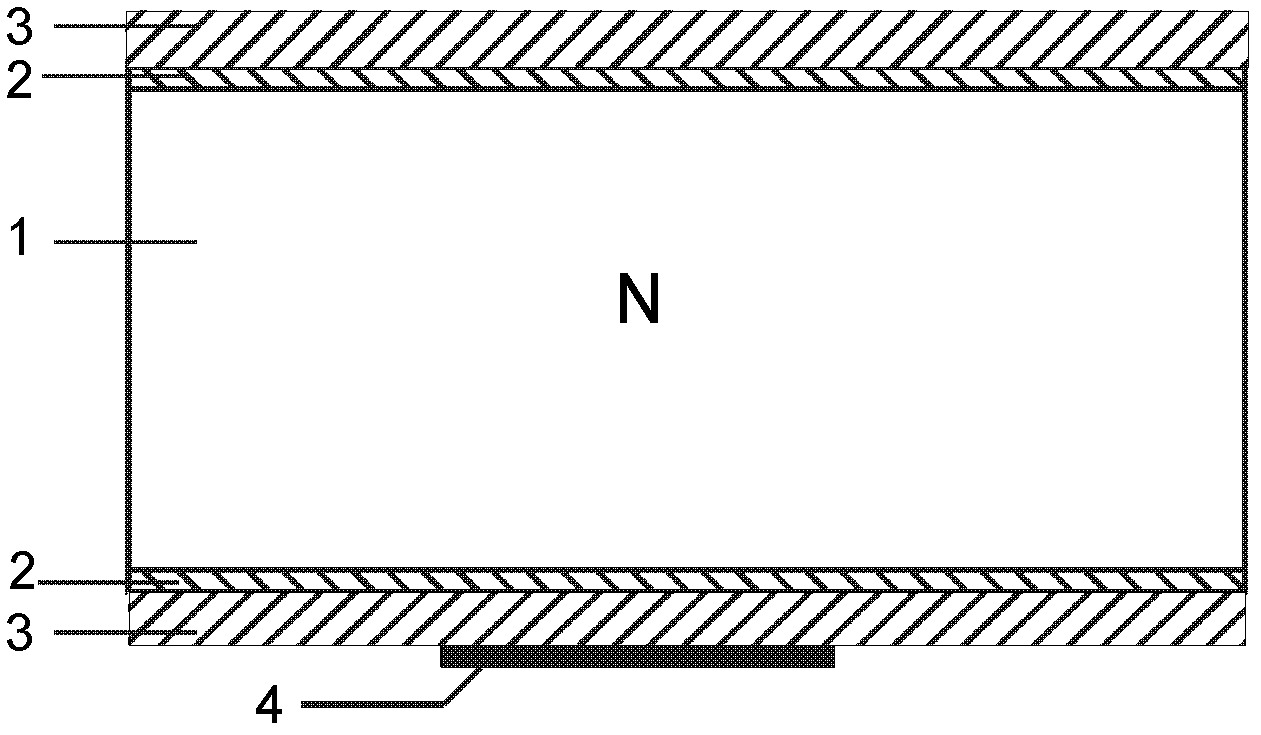

[0041] The HIT solar cell structure and preparation process of the heterogeneous floating junction back passivation, the basic idea is to deposit a P-type amorphous silicon layer 3 on the upper surface and the lower surface of the N-type crystalline silicon substrate 1 to form a heterogeneous P-N junction Structure, the floating of the P-N junction on the back of the N-type crystalline silicon substrate 1 is realized by vapor deposition of the insulating film layer 5, while the back electrode is still realized by N-type amorphous silicon deposition. The N-type amorphous silicon back electrode and the P-type amorphous silicon floating junction back passivation structure are strictly separated by the insulating film layer 5, which ensures a good floating junction back passivation effect.

[0042] First, unlike Sanyo's HIT battery process, this process deposits an amorphous silicon P-N heterostructure layer on the upper and lower surfaces of the N-type crystalline silicon substrat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More