Chip reflow method of semiconductor manufacturing process

A manufacturing process and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of low withstand voltage, large influence of device parameters, and inability to increase the withstand voltage value of the chip, so as to improve the withstand voltage of the chip. Value, technologically simple and feasible effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

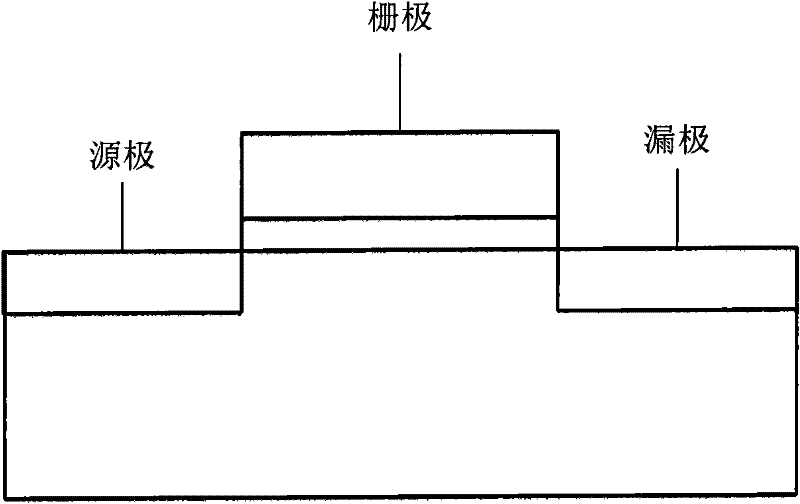

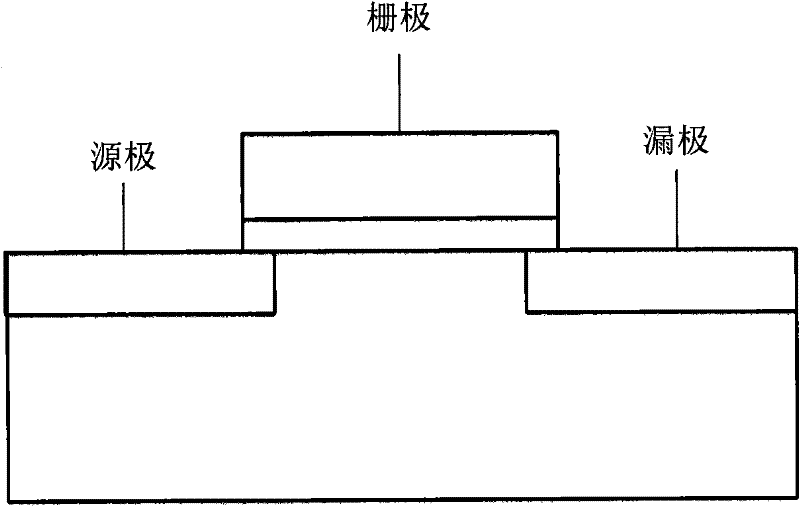

[0025] During the invention process, the inventor found that in the semiconductor manufacturing process flow, the higher the temperature in the reflow process, the more the lateral diffusion of the source and drain, resulting in a lower chip withstand voltage value. see Figure 1A ~ Figure 1B , Figure 1A A schematic diagram showing the structure of the source and drain before reflow, Figure 1B A schematic diagram of the structure after lateral diffusion of source and drain after reflow.

[0026] The invention provides a chip reflow method in a semiconductor manufacturing process. By changing the reflow temperature, the lateral diffusion of source and drain is reduced, and the purpose of improving the withstand voltage value of the entire chip is achieved. At the same time, the process is simple and feasible, and no additional process steps are added.

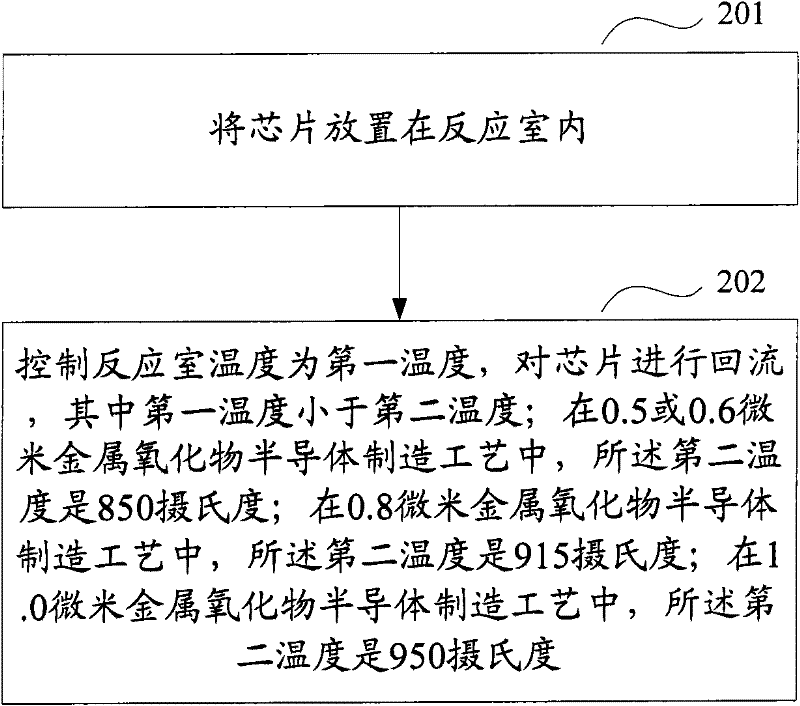

[0027] The solution of the present invention will be described in detail below in conjunction with the accompanying drawin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More