Manufacturing method of transistor

A fabrication method and transistor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as device performance instability, and achieve the effects of improving stability, complete surface structure, and reducing leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

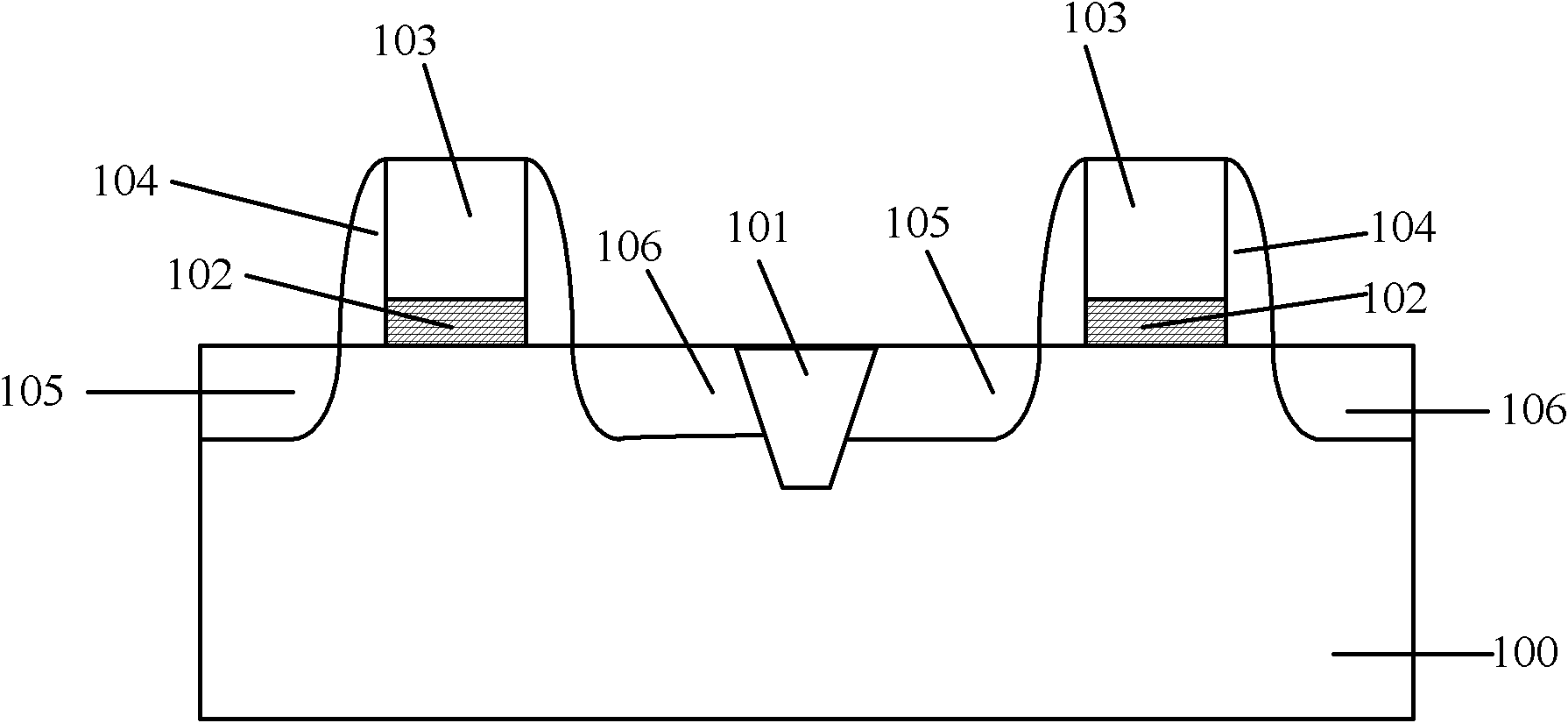

[0042] The transistor produced by the existing method has leakage current, and the performance of the device is unstable. After research by the inventors, it is found that the above problems are caused by the poor adhesion of the high-K dielectric layer to the gate dielectric layer and the sidewalls. Specifically, combine image 3 , during the process of removing the dummy gate 103, the gate dielectric layer 102 and the spacer 104 are damaged, so that the formed high-K dielectric layer 108 ( Figure 4 ) has poor adhesion to the sidewall 102 and the gate dielectric layer 108, which causes the leakage current of the transistor, thereby affecting the performance of the device.

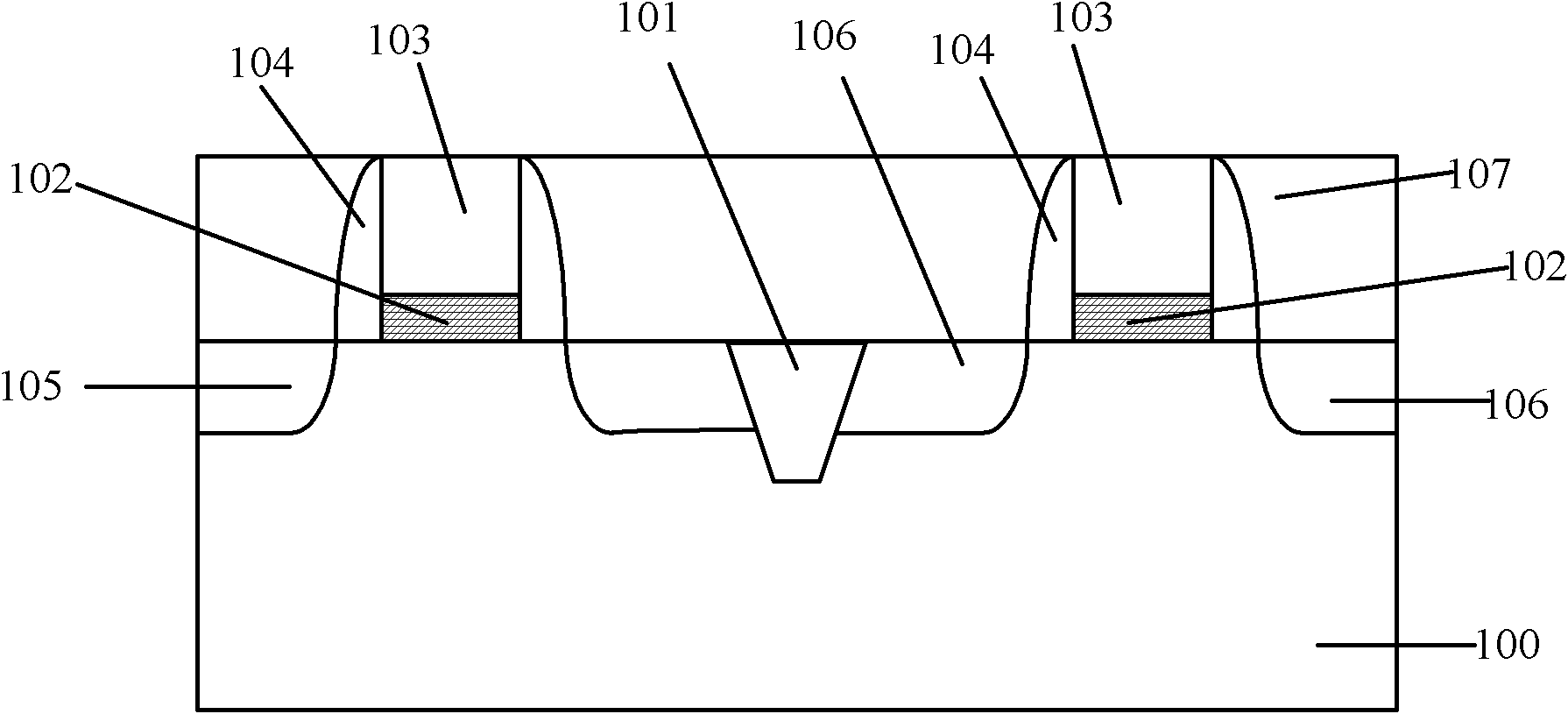

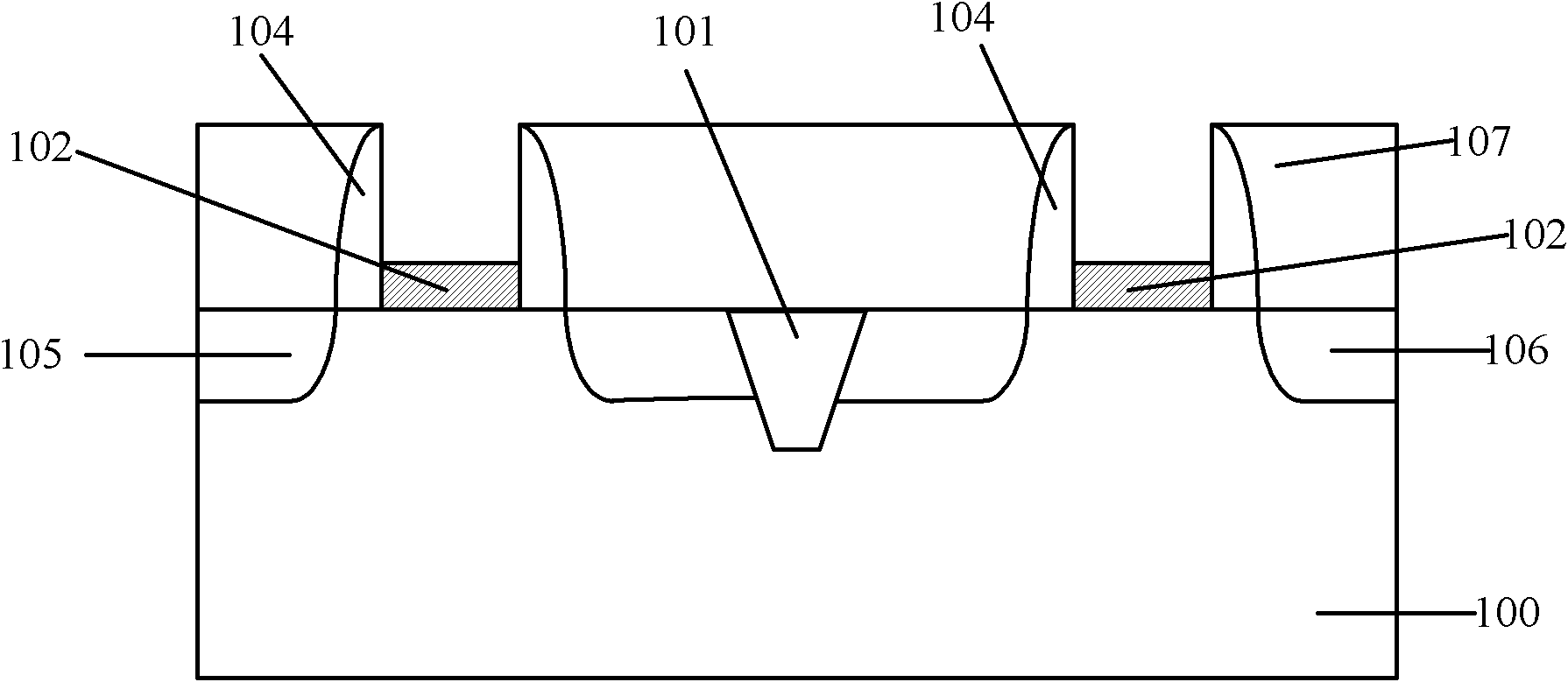

[0043] In order to solve the above problems, the inventor proposes a method for making a transistor, please refer to Figure 6 The schematic flow chart of the transistor manufacturing method of the present invention shown, the method includes:

[0044] Step S1, providing a semiconductor substrate, a sa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More