Read-Only Cache Memory for Embedded Chips

An embedded chip and high-speed buffering technology, which is applied in the direction of memory systems, instruments, input/output to record carriers, etc., can solve the problems of inconvenient user configuration, increased cache memory (CACHE complexity, increased chip area and power consumption, etc.) , to achieve the effect of improving performance and practicability, replacing efficiency and resource overhead balance, and reducing module power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0034] Embodiment: A kind of read-only cache memory applied to embedded chip

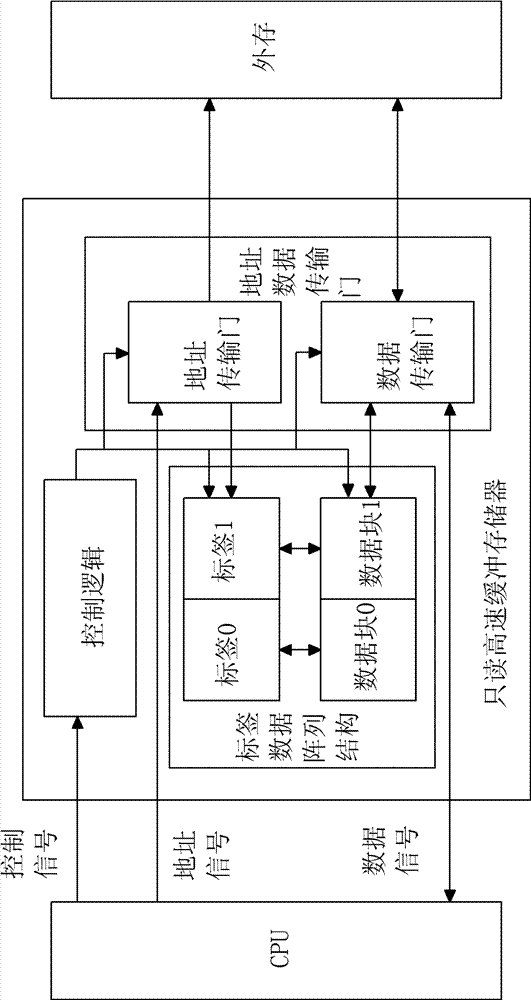

[0035] like figure 1 As shown, the read-only cache memory is composed of three parts: tag data array structure, control logic module, and address data transmission gate. The three parts are described below:

[0036] 1. Tag data array structure

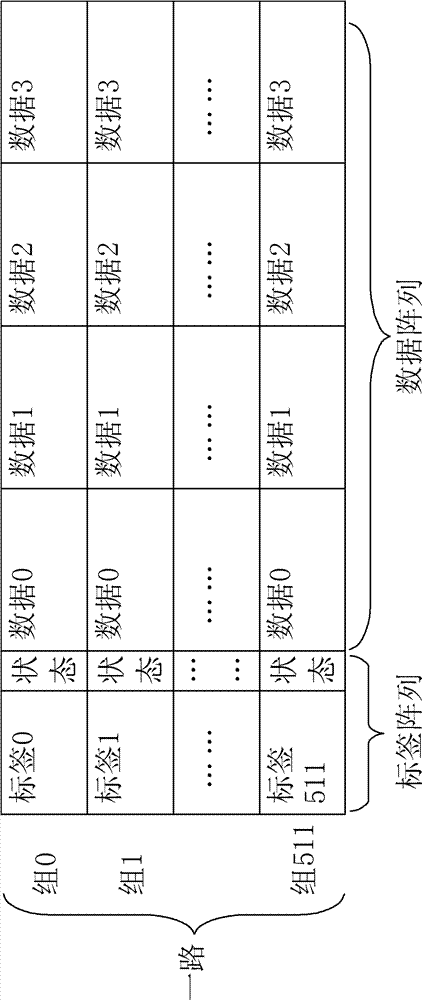

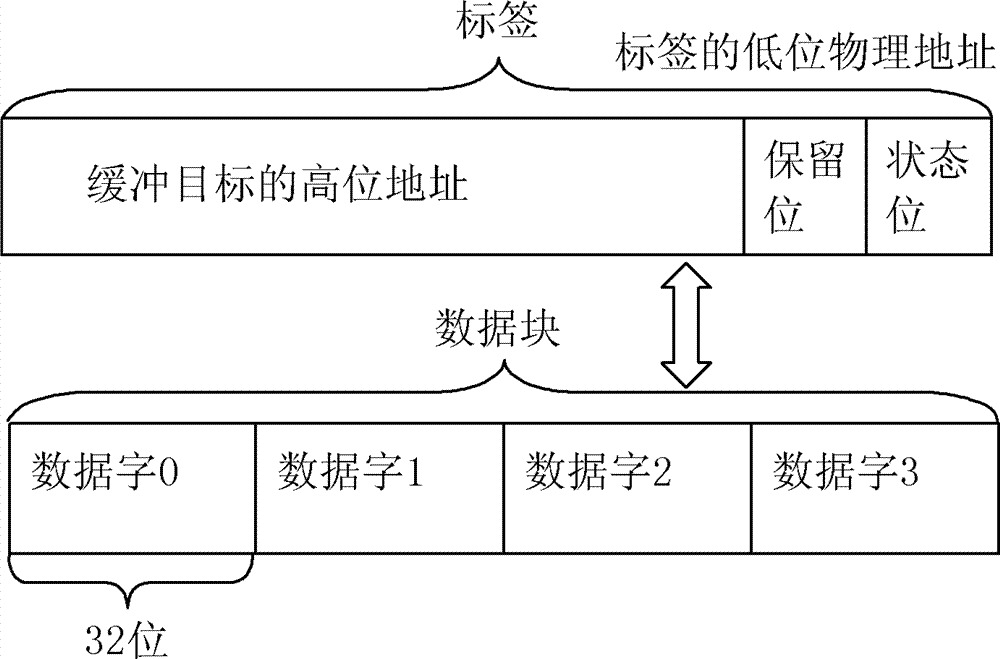

[0037] like figure 2 and image 3 As shown, the tag data array structure refers to the tag data array structure defined on the SRAM memory bank for read-only buffering. The tag data array structure is composed of at least two tag data arrays, each tag data array is composed of several groups of tag data, and each group of tag data is composed of tags and data blocks. figure 2 Only draw a schematic diagram of the label data array of a certain road (other roads are basically the same as the schematic diagram of this road), where group 0, group 1 and group 511 represent groups, group 0 is composed of label 0 and data blocks, and data blocks are composed of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More