Preparation method for backgate thin film transistor storage

A thin-film transistor and memory technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of thin film compactness and lack of uniformity of large-area components, and achieve improved large-area uniformity and clear interface. , to achieve the effect of integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The invention will be described in detail below in conjunction with the accompanying drawings and specific examples.

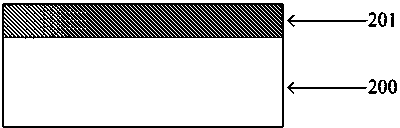

[0032] Step 1: Select a heavily doped P-type single crystal silicon wafer with a resistivity of 0.008-0.100 Ω cm as the substrate, and clean the silicon wafer through a standard RCA cleaning process, and then remove the surface of the silicon wafer with hydrofluoric acid oxide layer. refer to figure 1 , the cleaned silicon wafer is shown as 200 in the figure.

[0033] Step 2: On the cleaned silicon wafer, use ALD method to deposit and grow Al 2 o 3 film, such as figure 1 Shown on the 201st floor. Al 2 o 3 The thickness of the film is 15-200nm; during the deposition process, the substrate temperature is controlled at 100-300 oC between; growing Al 2 o 3 The reaction sources are trimethylaluminum and water vapor.

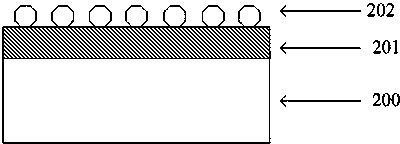

[0034] Step 3: Using ALD method on Al 2 o 3 Deposit a layer of Ru nanocrystals on the film, such as figure 2 Shown in 202. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More