Manufacturing method and structure of asymmetric high-voltage MOS device

A technology of MOS devices and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of narrowing the cross-section of the current path, increasing the equivalent path resistance, and reducing the driving current. Effects of equivalent path resistance, increased drive current, and convenient lateral size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described below with reference to the manufacturing method and structure of the asymmetric high-voltage NMOS device of the embodiment of the present invention. For the manufacturing method and structure of the asymmetric high-voltage PMOS device, the doping types of the body region, drift region, and source-drain region are just opposite to those of the asymmetric high-voltage NMOS device, so this patent does not make further descriptions.

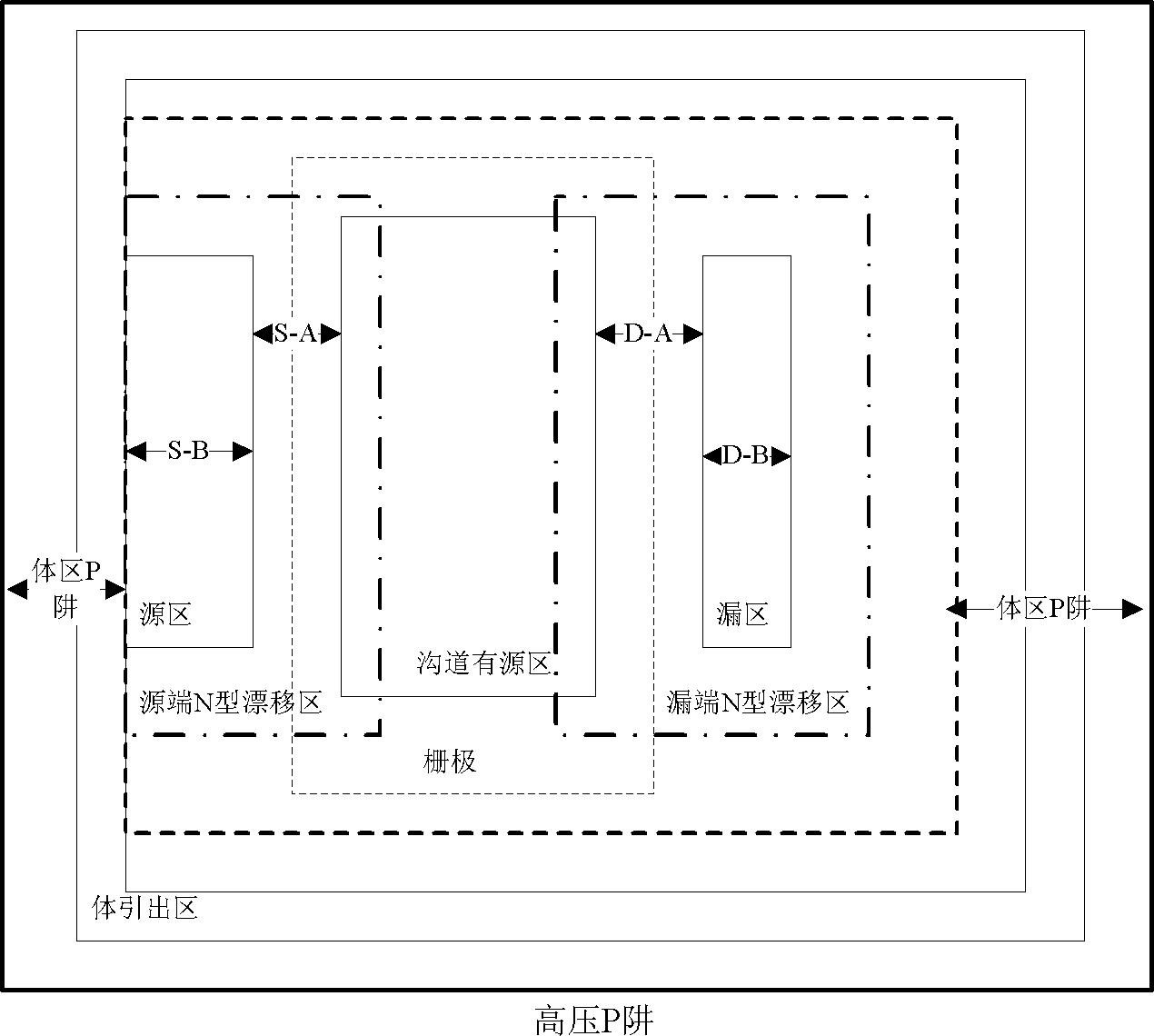

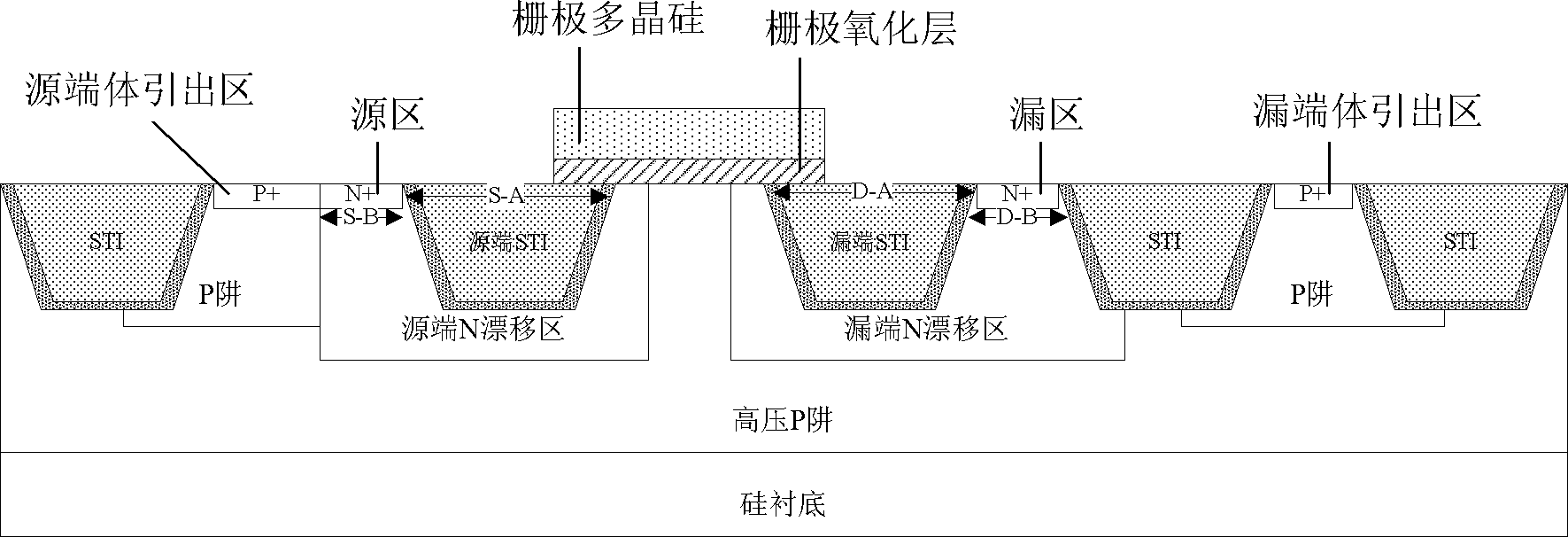

[0024] Such as figure 2 Shown is a schematic diagram of the structure of an asymmetric high-voltage NMOS device according to an embodiment of the present invention. The method for manufacturing an asymmetric high-voltage NMOS device according to an embodiment of the present invention includes the following steps:

[0025] Step 1: Change the layout during the layout design process. Such as figure 1 Shown, the embodiment method of the present invention and figure 1 The only difference in the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More