Design and method of domain layout of 14-bit integrated circuit DAC (Digital to Analog Converter) current source array

A current source array and integrated circuit technology, applied in the direction of digital-to-analog converters, etc., can solve the problems that cannot meet the requirements of high conversion accuracy and high speed, do not consider the spatial distribution, and the conversion accuracy requirements are not very high, etc., to achieve good heat resistance Gradient effect, spurious-free signal-to-noise ratio, effect of spurious-free dynamic range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

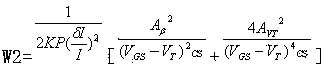

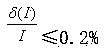

Method used

Image

Examples

Embodiment Construction

[0048] Below in conjunction with embodiment the present invention is described in further detail:

[0049] The 14-bit integrated circuit DAC current source array includes a main array formed by a plurality of current sources neatly arranged. The main array is divided into four main quadrants according to the upper and lower midlines and the left and right midlines. The four main quadrants are respectively the upper left main quadrant, Lower Left Main Quadrant, Upper Right Main Quadrant, and Lower Right Main Quadrant (eg Figure 4 shown).

[0050] Each main quadrant is further divided into four sub-quadrants according to the upper and lower midlines and the left and right midlines, such as Figure 5 As shown, the auxiliary quadrant located in the upper left of the upper left main quadrant is divided into the left half and the right half. The left half includes areas 1 to 8, and areas 1 to 8 are distributed from left to right and from top to bottom. 1. Area 5, Area 6, Area 2, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More