A 10-bit high-precision DAC current source array and its layout method

A technology of current source array and layout method, used in electrical components, digital-to-analog converters, physical parameter compensation/prevention, etc., can solve problems such as systematic errors, poor matching of high and low current sources, and large random errors. , to achieve the effect of reducing chip area, accurate replication, and good monotonicity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The technical solutions provided by the present invention will be described in detail below in conjunction with specific examples. It should be understood that the following specific embodiments are only used to illustrate the present invention and are not intended to limit the scope of the present invention.

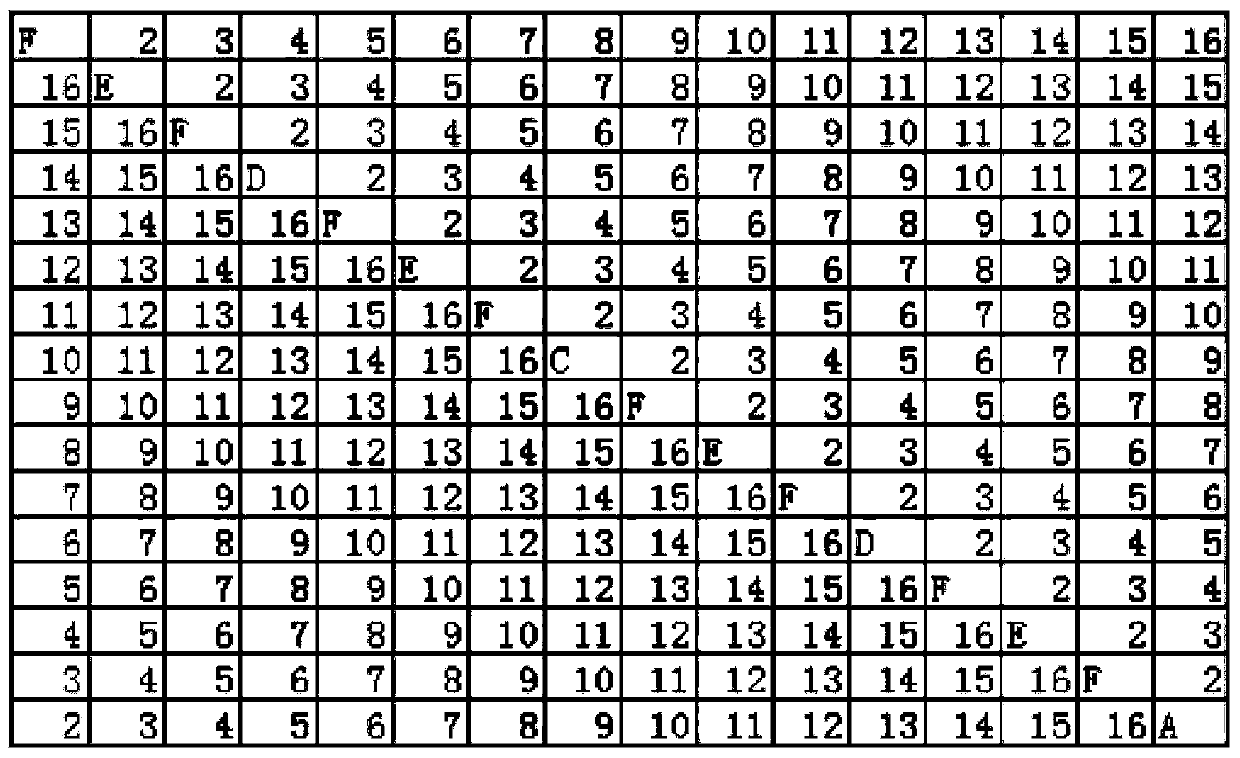

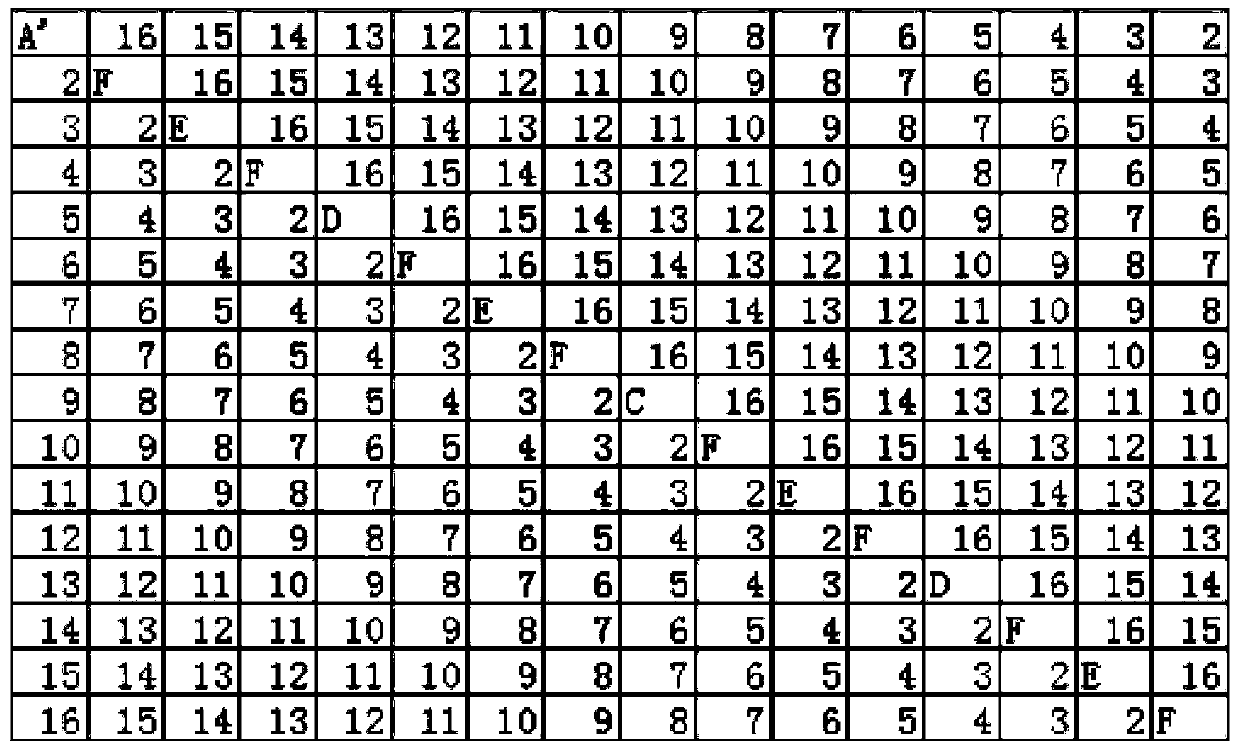

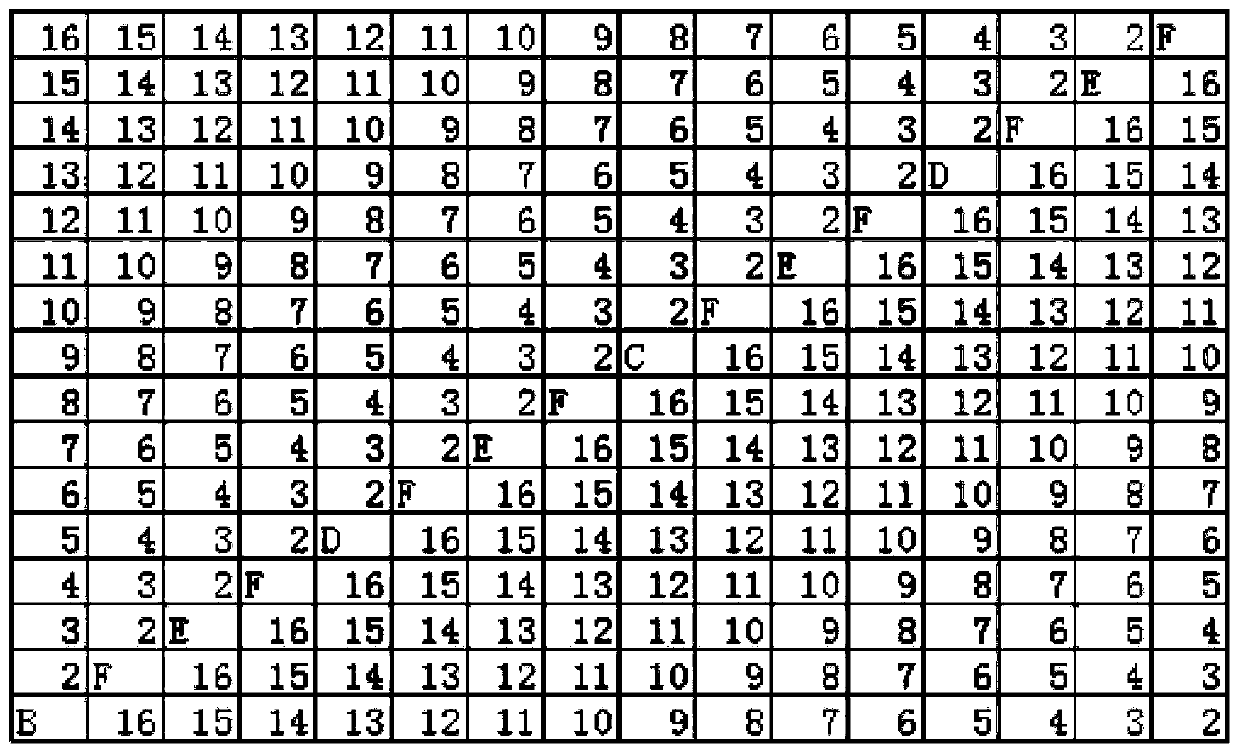

[0033] The 10-bit current steering DAC current source array requires a total of 1024 current source elements to form a 32*32 array. The present invention first generates a 16*16 sub-array Z waiting for rotation, mirroring, replacement, etc., and passes it through After multiple transformations, each 16*16 sub-array is obtained and combined into a final array according to a specific positional relationship. The present invention lays out an 8-bit high-precision DAC current source array through the following steps:

[0034] Step 1: Generate 16*16 (row*column) subarray Z.

[0035] Arrange the numbers 1-16 in a row from left to right in ascending order, then copy the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More