Instruction optimization processor for RSA encryption algorithm

A technology of instruction optimization and encryption algorithm, applied in concurrent instruction execution, electrical digital data processing, instruments, etc., can solve the problems of limited acceleration effect, weak scalability, difficult combination, etc., and achieve the goal of reducing instruction cycle and saving resource consumption Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

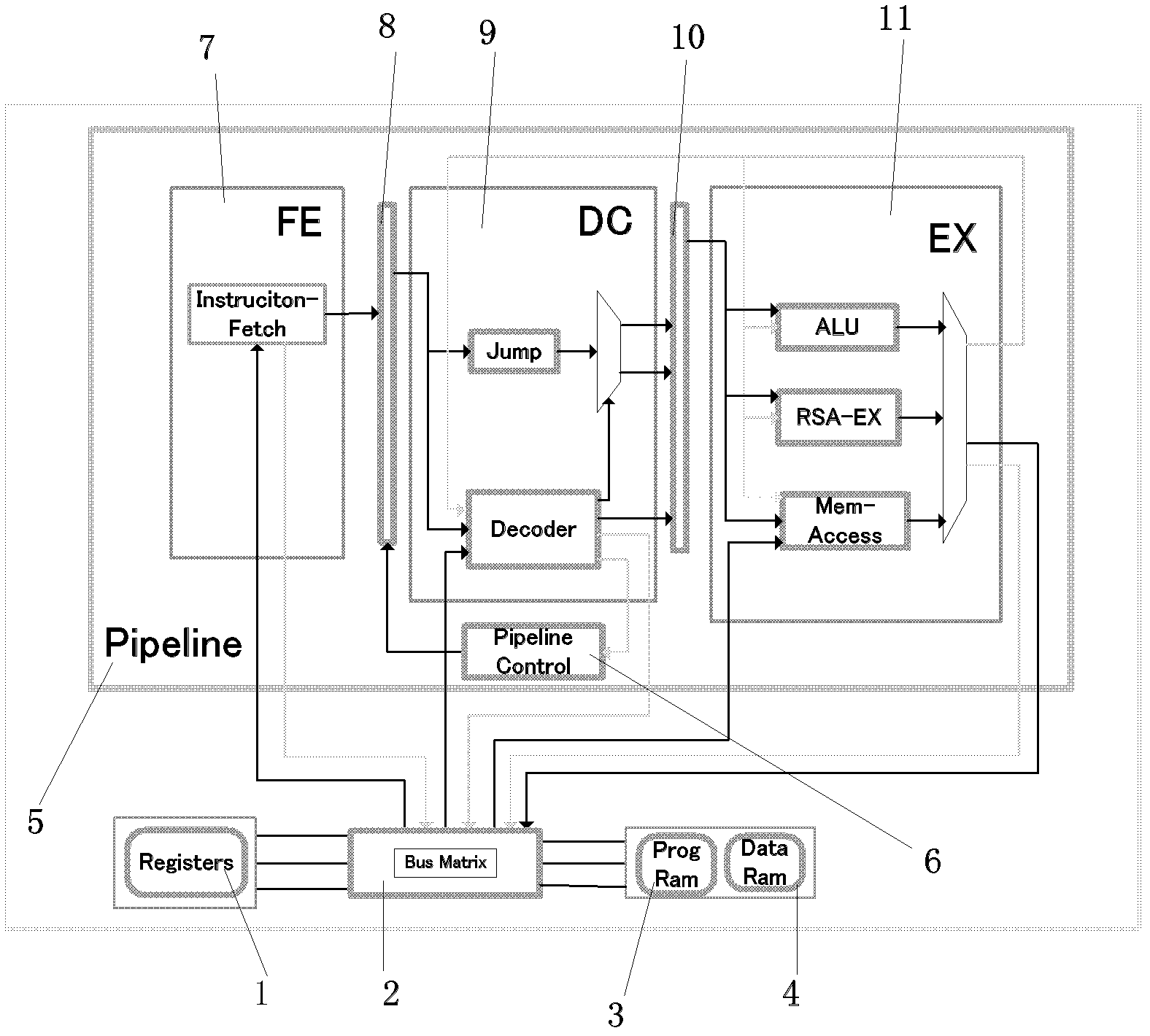

[0042] figure 2 Among them, an instruction set processor model designed according to the extended instruction set, which realizes the above-mentioned extended instructions in hardware logic, so it can be used to accelerate the RSA encryption algorithm. The processor model mainly consists of register file 1, bus matrix 2, code memory 3, data memory 4, instruction pipeline 5, pipeline control component 6, pipeline fetching component 7, pipeline internal bus I, pipeline decoder component 9, and pipeline internal Composed of bus II10 and pipeline execution unit 11, the address space of data memory 4 is defined in the range of 0x0000-0x7FFF, with a size of 32K;

[0043] The code memory 3 address space is defined in the range of 0x8000-0xFFFF, with a size of 32Kbytes;

[0044] Register file 1 is mainly composed of 32 general-purpose registers, 1 fetch regi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More