Signed multiply-accumulate algorithm method using adder tree structure

An adder tree and multiply-accumulate technology, which is applied to instruments, calculations, and electrical digital data processing, etc., can solve problems such as recalculation, and achieve the effect of small area and convenient expansion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

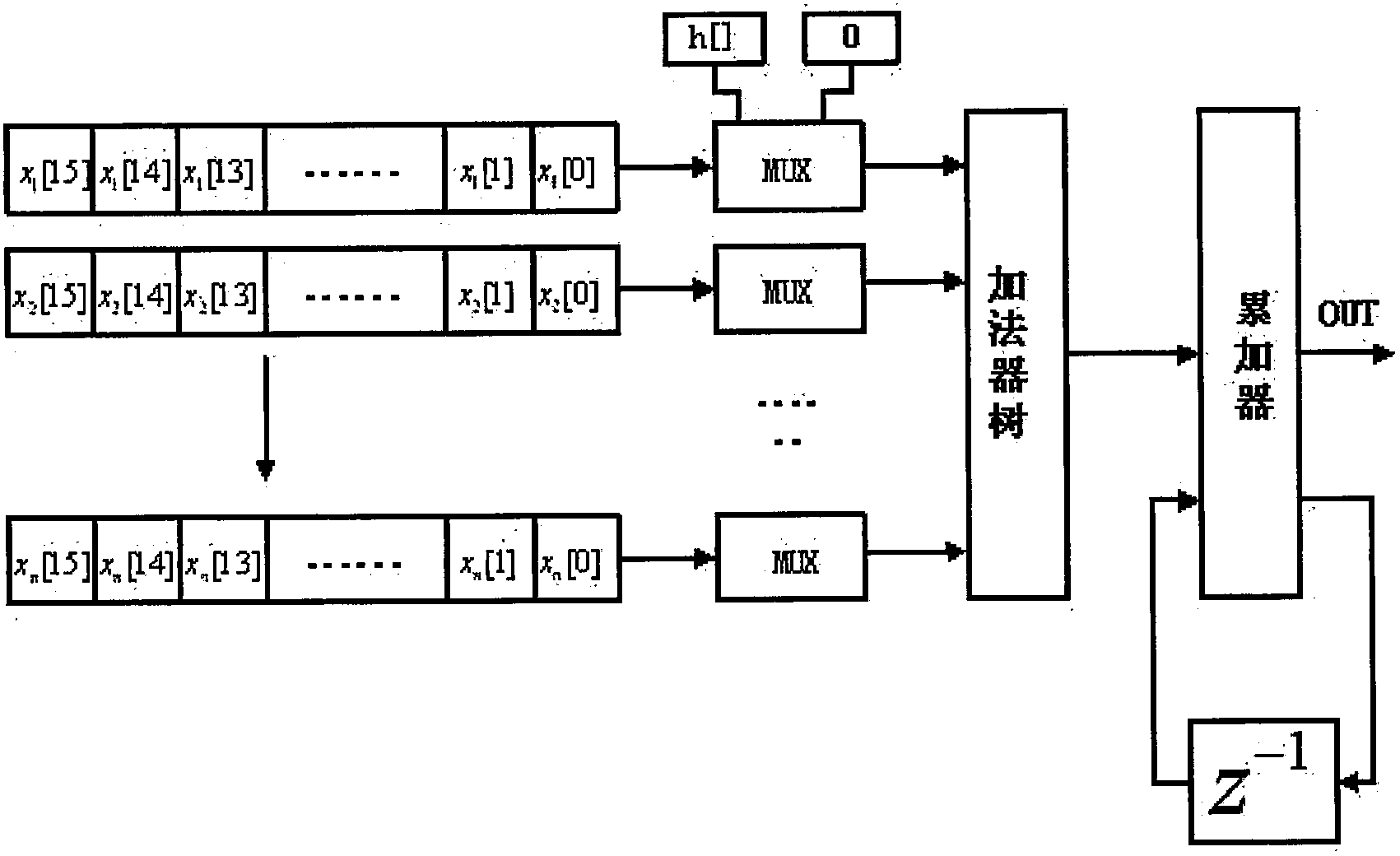

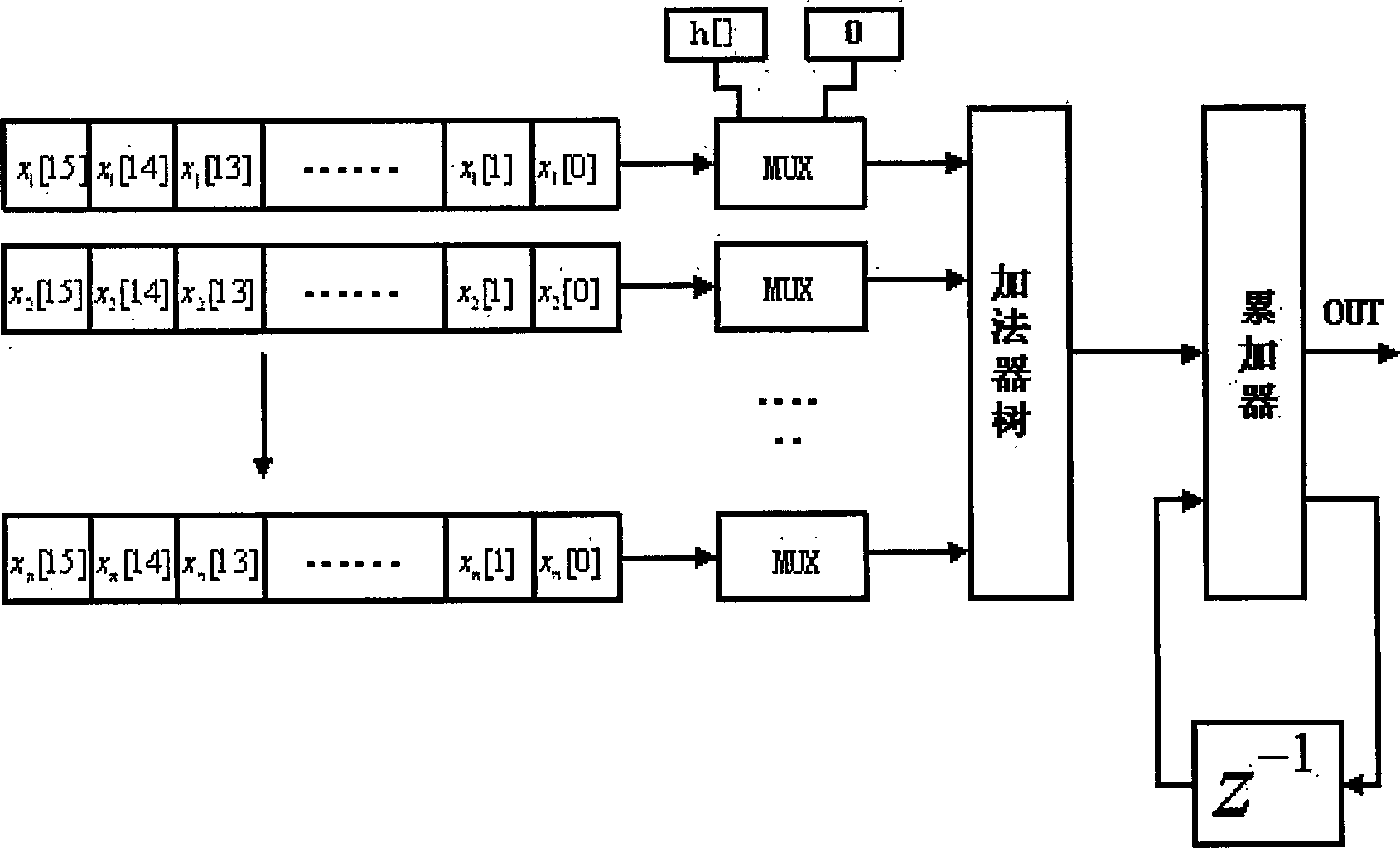

[0017] When considering the following multiply-accumulate calculation:

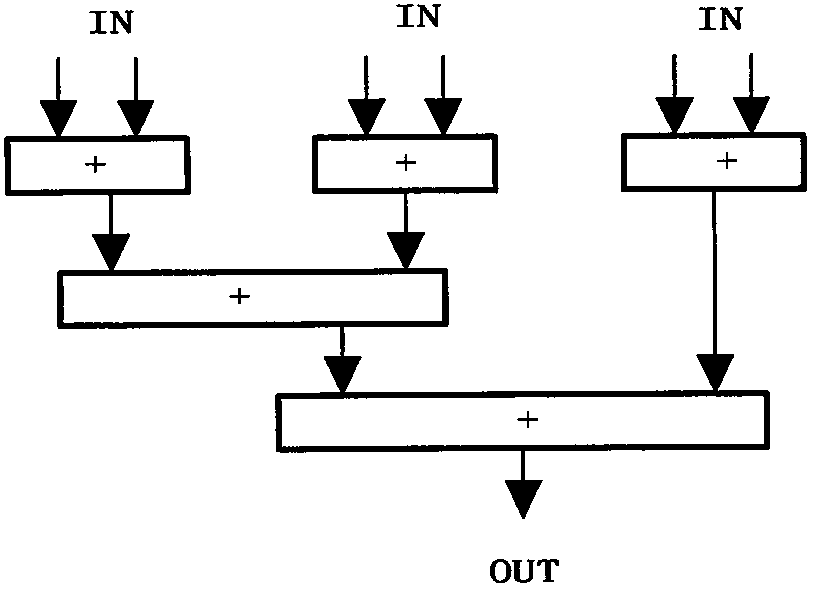

[0018] Get N=6, c and x all are the complement code operand of word length 8+1 sign bit. When multiplying the accumulator, the operand D[x] is first sent to the shift register Rx, and the operand c[n] and its {-c[n] 补} is sent to another register. Driven by the synchronous clock, all operands x are shifted to the right at the same time, and the data selection switches M1-M6 select the 6 operands input to the adder tree A1 according to the lowest bit of the R1-R6 shift register. c is still 0, for example: under a certain clock drive, the lowest bits of the six shift registers R1-R6 are [1, 1, 0, 1, 0, 1] respectively, then the six input terminals of the adder tree A1 The operands are {c[1], c[2], 0, c[4], 0, c[6]}. The adder tree A1 outputs the sum of the six operands, which is sent to the accumulator M1 and added to the previously shifted and accumulated value, and stored as a new value. After the ne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More