DMT (Discrete Multi-Tone)-based transmission method and device of high-speed 1553B communication bus

A technology of communication bus and sending device, applied in bus network, data exchange through path configuration, etc., can solve the problems of stability impact and high cost of the original system

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

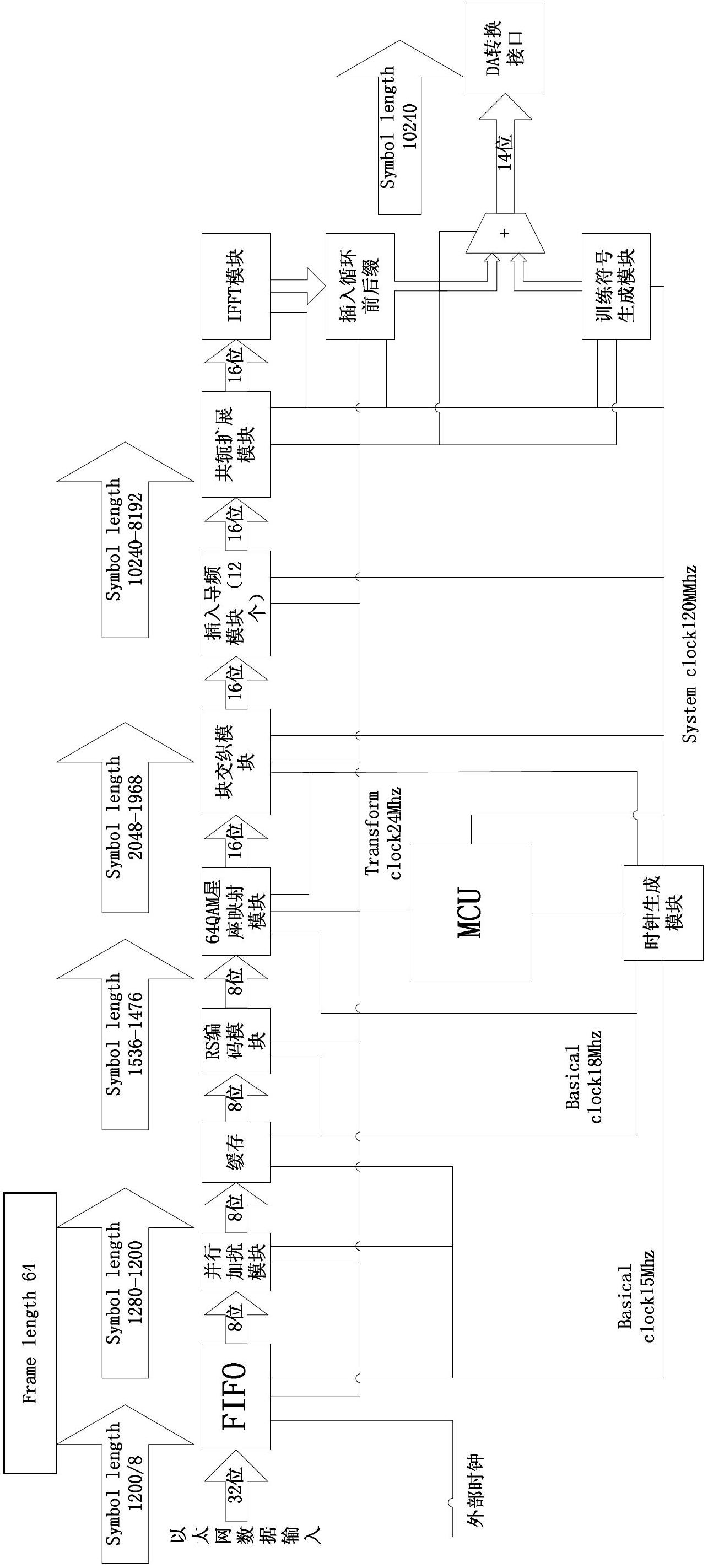

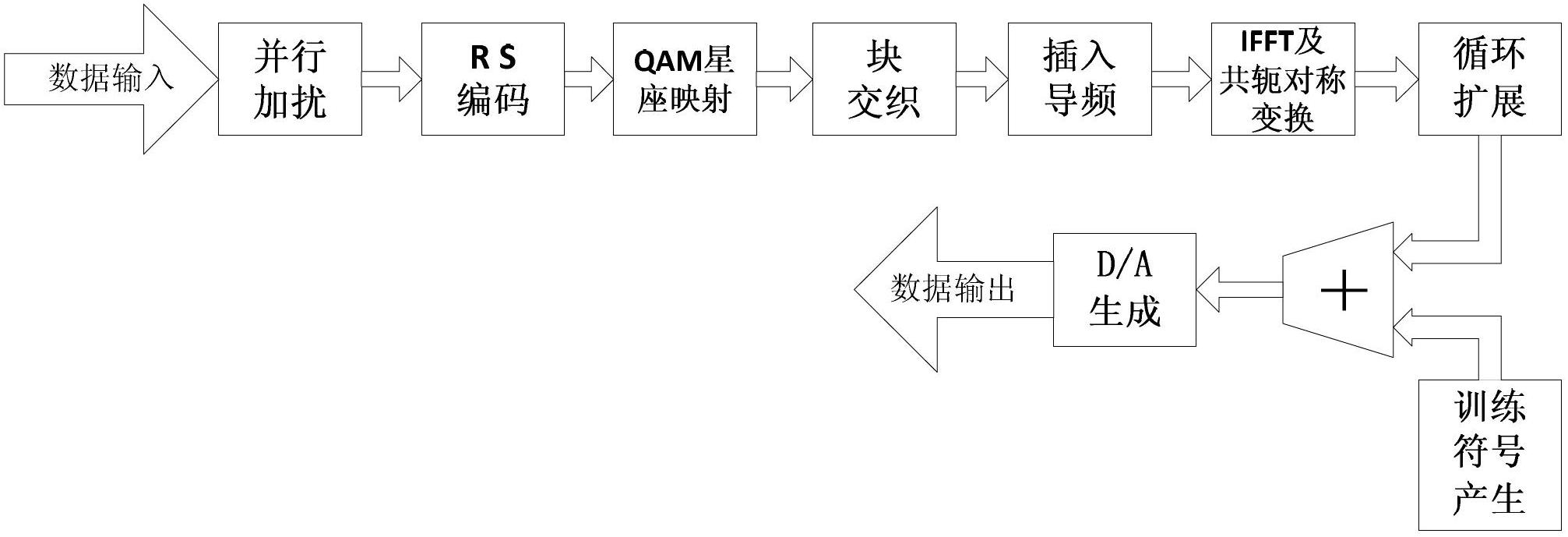

[0063] The cable used in the high-speed 1553B communication bus system developed by the present invention is similar to the twisted pair used in the ADSL (Asymmetric Digital Subscriber Line, hereinafter referred to as ADSL) system, which is 75 ohms. Therefore, the DMT modulation technology that has been maturely applied in ADSL technology is the core technology of the high-speed 1553B communication bus system. Using DMT technology, the broadband channel is decomposed into a large number of narrowband sub-channels. The frequency characteristics of each sub-channel are relatively flat, and the data rate that can be transmitted in each sub-channel is low. Using multi-channel parallel transmission technology, the total data rate can be Reach very high.

[0064] The design starting point of the high-speed 1553B communication bus system is to provide a high-speed data transmission channel for new high-speed devices connected to the bus while keeping the original bus system unchanged...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More