User description based programming design method on embedded heterogeneous multi-core processor

A multi-core processor and heterogeneous multi-core technology, applied in the direction of program control devices, etc., can solve problems such as application in the embedded field or propose effective solutions, and achieve the effect of reducing difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

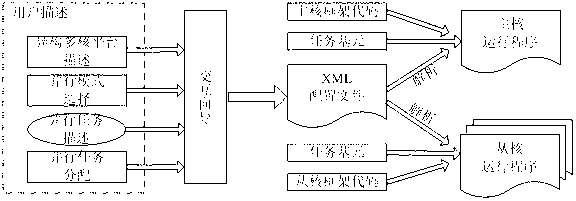

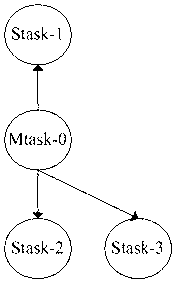

[0045] see Figure 1~4 , the parallel programming method based on user description on the embedded heterogeneous multi-core processor is characterized in that it includes the following steps: the user performs the description of the heterogeneous multi-core processor platform and tasks through the graphical interface configuration wizard, parallel mode setting, Creation and registration of primitive tasks, generation of task relationship graph (DAG) and static allocation of primitive tasks in heterogeneous multi-core processors, realizing the expression of processor platform characteristics, parallel requirements and task assignment in the form of configuration files (XML) and then embed the primitive tasks after the parallel parsing of the configuration file into the corresponding task label of the heterogeneous multi-core framework code, construct the corresponding serial source program, and finally generate the executable on the heterogeneous multi-core processor by call...

Embodiment 2

[0063] see Figure 1~5 , this embedded heterogeneous multi-core processor is based on the parallel programming method described by the user, and its operation steps are as follows:

[0064] 1. Analysis Parallelization

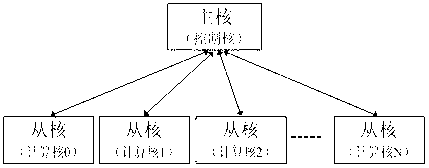

[0065] Analyze the application requirements in domain problems and abstract the problem framework to examine whether it is suitable for parallel processing, whether it can be decomposed into a series of smaller-scale different functional tasks that can be calculated at the same time, and then determine the parallel mode of dependencies between tasks. The embedded heterogeneous multi-core master-slave architecture can support the requirements of multiple parallel computing modes such as task seeding, pipeline, and divide-and-conquer.

[0066] 2. Heterogeneous multi-core processor platform description

[0067] The description includes the types of heterogeneous cores, instruction sets, number, operating frequency, storage space, and the compilation tool chain a...

Embodiment 3

[0087] Such as figure 1 , shown in 2, a schematic diagram of the principle framework of the present invention.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More