LDPC (Low Density Parity Check) encoding method based on FPGA (Field Programmable Gate Array) and used in CMMB (China Mobile Multimedia Broadcasting) exciter

A coding method and technology of an exciter, which are applied in error detection coding using multi-bit parity bits, error correction/detection using block codes, data representation error detection/correction, etc. Linear complexity, unrealistic implementation and other problems, to achieve the effect of simplifying logical operation operations, reducing coding complexity, and saving storage space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

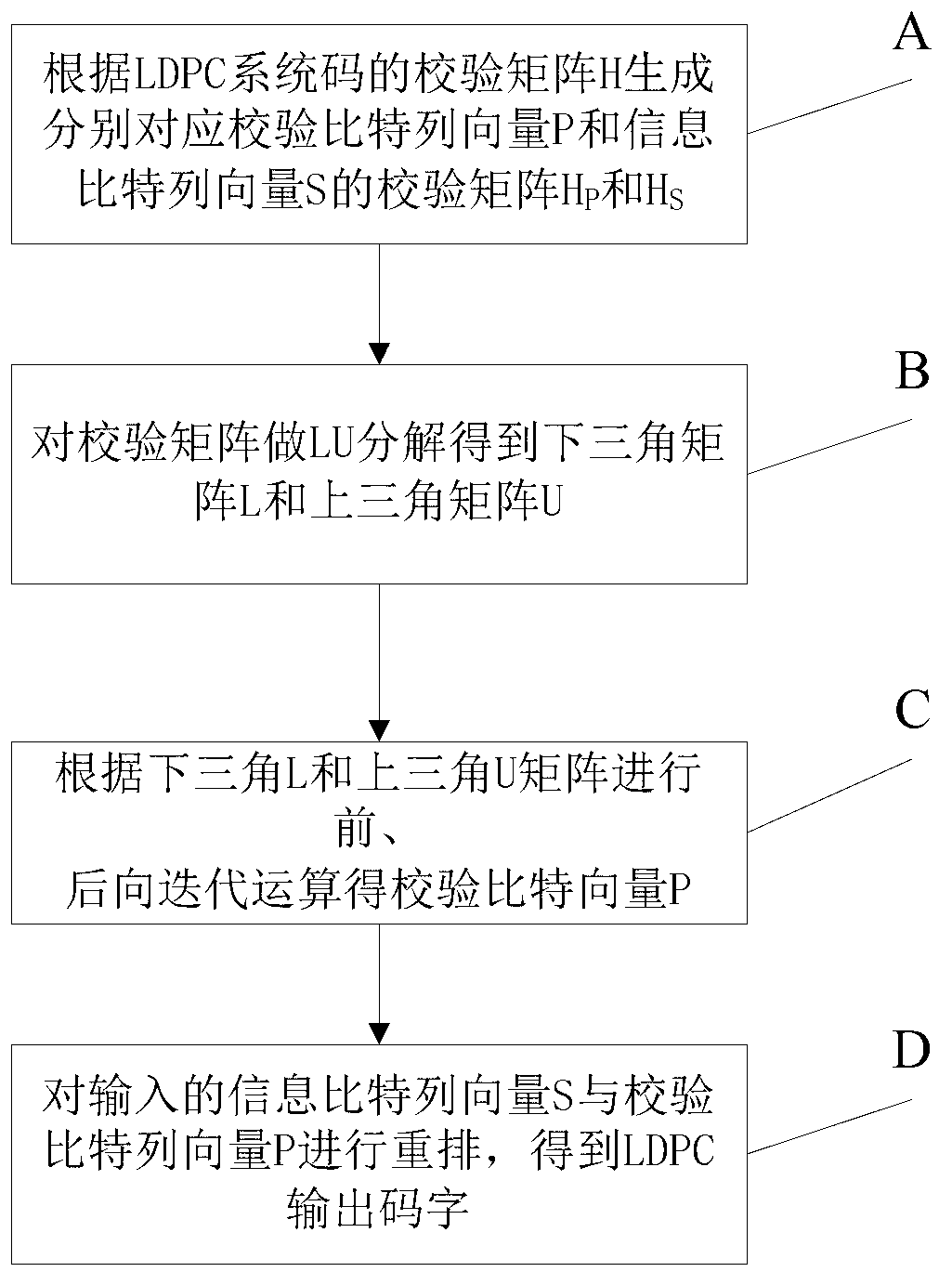

[0078] The specific embodiment of the present invention will be further described below in conjunction with accompanying drawing:

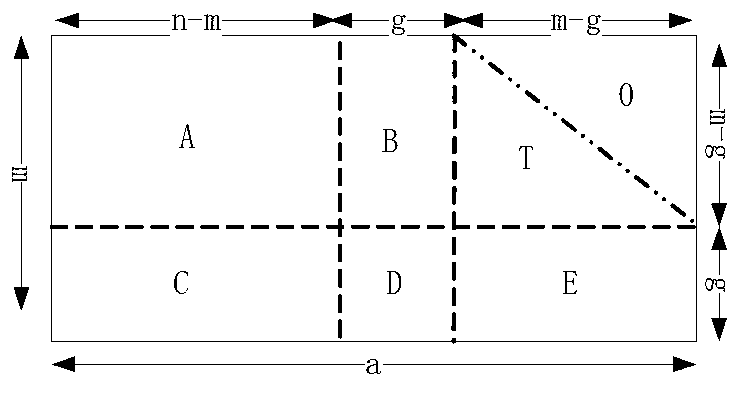

[0079] In the CMMB exciter, for different channels and transmission content, the LDPC code has two different code rates of 1 / 2 and 3 / 4 to choose from. If the code rate is selected, the information bit length for each LDPC encoding is fixed. The fixed length forming each codeword is 9216 bits. LDPC output code word C={c 0 , c 1 ,... c 9215} by the input information bit S={s 0 ,s 1 ,...s k-1} and parity bits P={p 0 ,p 1 ,…p 9215-K}, rearrange according to the following formula:

[0080] The description of the LDPC encoding module in the CMMB standard: the input information bit sequence vector S and the check bit sequence vector P are rearranged to obtain the LDPC output codeword.

[0081] C COL _ ORDER ( i ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More