Three-layer anti-counterfeit label pcb board and its preparation process

A technology for PCB boards and anti-counterfeiting labels, which is applied to printed circuits connected with non-printed electrical components, printed circuits assembled with electrical components, etc. It can solve the problem that surface treatment cannot be gold-plated, cannot be fixed accurately, and three-layer boards cannot Accuracy and other issues to achieve the effect of reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

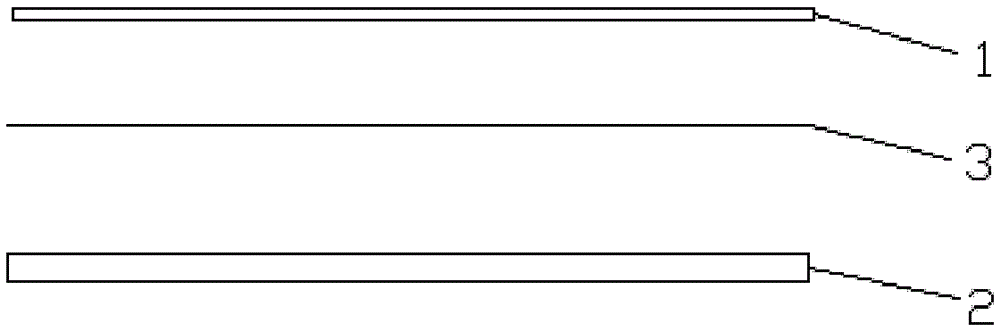

[0022] A three-layer anti-counterfeiting label PCB board, which includes a light board 1 and a core board 2 arranged in parallel to each other, ink and lines are printed on both sides of the core board, and a parallel arrangement is also arranged between the light board and the core board. There is an insulating layer 3 .

[0023] The insulating layer is made of epoxy glass cloth material.

[0024] The light board is made of glass fiber material.

[0025] A preparation process for a three-layer anti-counterfeit label PCB board, which comprises the following steps:

[0026] ① Core board cutting, that is, cutting the substrate into a core board of a set size according to needs;

[0027] ② Drill and hole the core board;

[0028] ③ Set up lines on both sides of the core board;

[0029] ④Electroplating the core board, that is, copper-plating the entire core board;

[0030] ⑤ Etching the core board, that is, displaying the circuit diagram required on the surface of the core boa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com