Method and framework for optimum grading of the inside of high performance static state random access memory

A static random and memory technology, applied in the direction of static memory, digital memory information, information storage, etc., can solve the problem of no increase in throughput, achieve the effects of reduced delay, reduced driving capability requirements, and optimal performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

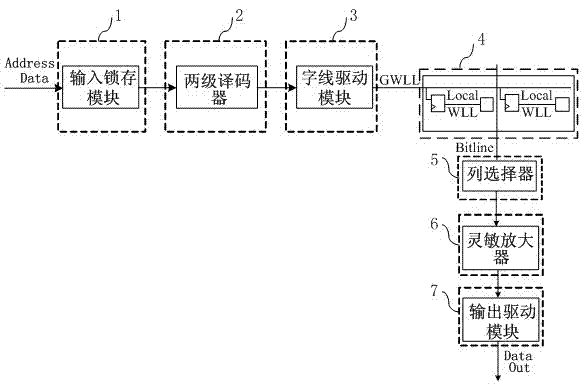

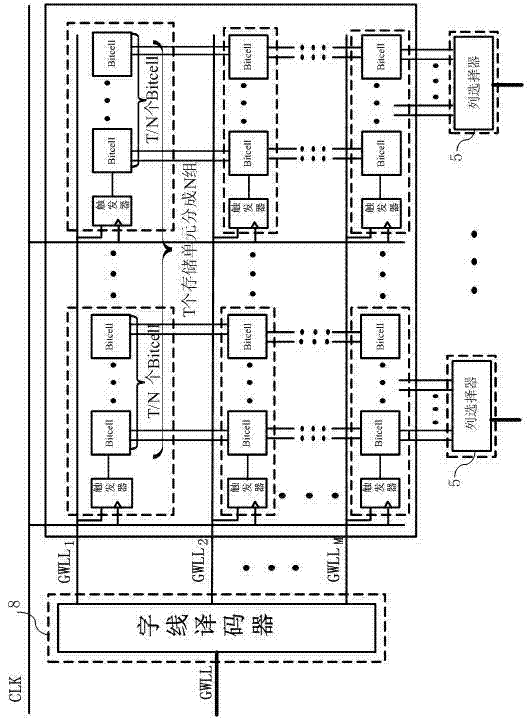

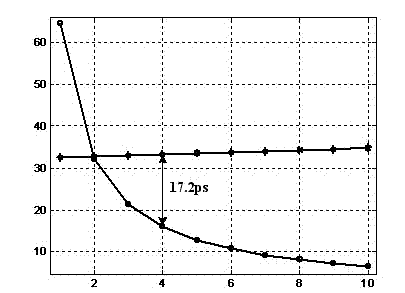

[0011] A method for internal optimal grading of a high-performance SRAM, the method comprising: inserting a flip-flop between the global word line GWLL and the local word line Local WLL, dividing each row of the memory array 4 into N equal to the number of memory cells Bitcell memory modules, so that each memory module contains approximately equal parasitic capacitance, so the problem of the second-level delay short board can be avoided. With this implementation, each flip-flop only needs to drive a small number of storage units Bitcell, which can greatly reduce the size and clock load of the flip-flop. If the total number of the storage unit Bitcell of each row of the storage array 4 is T, the storage unit Bitcell of each row of the storage array 4 is divided into N storage modules, then the number of the storage unit Bitcell included in each storage module is T / N, one flip-flop corresponds to T / N storage units Bitcell in the storage module. Such as figure 1 , 2 shown.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More